# Application of VSI-EBG Structure to High-Speed Differential Signals for Wideband Suppression of Common-Mode Noise

Myunghoi Kim, Sukjin Kim, Bumhee Bae, Jonghyun Cho, Joungho Kim, Jaehoon Kim, and Do Seob Ahn

In this paper, we present wideband common-mode (CM) noise suppression using a vertical stepped impedance electromagnetic bandgap (VSI-EBG) structure for high-speed differential signals in multilayer printed circuit boards. This technique is an original design that enables us to apply the VSI-EBG structure to differential signals without sacrificing the differential characteristics. In addition, the analytical dispersion equations for the bandgap prediction of the CM propagation in the VSI-EBG structure are extracted, and the closed-form expressions for the bandgap cutoff frequencies are derived. Based on the dispersion equations, the effects of the impedance ratio, the EBG patch length, and via inductances on the bandgap of the VSI-EBG structure for differential signals are thoroughly examined. The proposed dispersion equations are verified through agreement with the full-wave simulation results. It is experimentally demonstrated that the proposed VSI-EBG structure for differential signaling suppresses the CM noise in the wideband frequency range without degrading the differential characteristics.

Keywords: Common-mode noise, differential signal, electromagnetic bandgap, EBG, stepped impedance, VSI-EBG

#### I. Introduction

In high-speed board design, differential signaling has been widely used for reliable data transmissions through Gbps data links, such as a high-definition multimedia interface (HDMI), a mobile high-definition link (MHL), or a universal serial bus (USB) 3.0. Differential signaling is considered a noise-tolerant signaling scheme due to its essential characteristics of balanced signals. In practical high-speed boards and cables, however, a common-mode (CM) noise cannot be prevented because of the imperfections of real differential channels resulting from a transceiver mismatch and a process variation, such as unbalanced geometries and asymmetrical material properties [1]-[3]. Even from a slight imbalance in the differential channels, a substantial amount of CM noise might be produced in the wideband frequency range. The inevitable CM noise over a wide frequency range seriously degrades the performances of the high-speed systems. Furthermore, the CM noise might cause a serious electromagnetic interference issue through cables attached to differential channels [4], [5]. Therefore, it is essential to suppress the broadband CM noise in the high-speed board.

To mitigate the wideband CM noise in gigahertz (GHz) differential signals, CM suppression filters using defected ground structures (DGSs) was proposed in [6], [7]. The previous approaches present wideband suppression of the CM noise in the GHz frequency range, which is difficult to achieve using the discrete CM choke. However, the filtering performances are sensitive to the metal plane below the

$Manuscript\ received\ Dec.\ 24, 2012;\ revised\ Apr.\ 3, 2013;\ accepted\ Apr.\ 11, 2013.$

Myunghoi Kim (phone: +82 42 860 1763, mhkim80@etri.re.kr), Jaehoon Kim (jhkim@etri.re.kr), and Do Seob Ahn (ahnds@etri.re.kr) are with the Broadcasting & Telecommunications Media Research Laboratory, ETRI, Daejeon, Rep. of Korea.

Sukjin Kim (sukjinkim@kaist.ac.kr), Bumhee Bae (bhbae@kaist.ac.kr), Jonghyun Cho (jonghyun.cho@kaist.ac.kr), and Joungho Kim (mhkim80@kaist.ac.kr) are with the Electrical Engineering, KAIST, Daejeon, Rep. of Korea.

http://dx.doi.org/10.4218/etrij.13.0112.0875

patterned ground plane, thus not suitable to the multilayer structure. The patterned ground planes act like slot antennas that might radiate CM noise. To overcome such drawbacks, researchers are considering the application of electromagnetic bandgap (EBG) structures to the differential signals. The EBG structures in [8]-[13] were introduced to suppress the wideband noise in the parallel plate waveguide (PPW) for the power distribution networks. Works [14]-[16] extended the use of the EBG structures from the PPW noise suppression to the CM noise suppression in differential lines. It was proven in [14]-[16] that the application of the EBG structures successfully suppress the CM noise in high-speed differential signals. However, the previous EBG structures have limitations regarding design requirements, reliability, and cost. For the approaches presented in [14], [15], the stopband of the EBG structure is too narrow to mitigate the wideband CM noise induced by the skew between the GHz differential signals. For the EBG structure shown in [16], the usage is limited by the low temperature co-fired ceramic technology and the blind via structure, which are sensitive to the manufacturing process and highly increase the manufacturing cost. Therefore, a new method to suppress wideband CM noise in high-speed boards that has a low cost and a high manufacturing reliability is required.

In this paper, we present the vertical stepped impedance EBG (VSI-EBG) structure to suppress wideband CM noise for high-speed differential signals in multilayer printed circuit boards (PCBs). This work extends the application of the VSI-EBG structure introduced in [17] to differential signals. The effects of the VSI-EBG structure on the common and differential characteristics are explored. Dispersion analysis is used to predict the bandgap and investigate the design parameter effects of the VSI-EBG structure. Based on the analysis results, we obtain an improved and optimized stopband bandwidth. The performances of the proposed VSI-EBG structure are experimentally verified through extensive measurements.

# II. VSI-EBG Structure for Differential Signaling

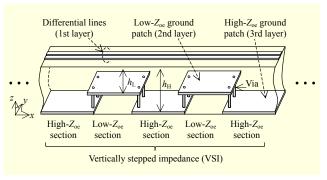

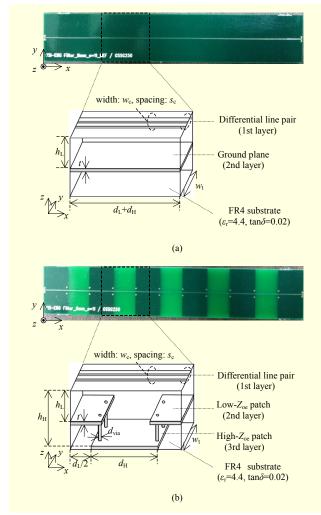

The proposed VSI-EBG structure for differential signaling consists of a differential line pair, ground patches for the low- $Z_{oe}$  (even-mode characteristic impedance,  $Z_{oe}$ ), and ground patches for the high- $Z_{\infty}$ , as shown in Fig. 1. The differential line pair on the low- $Z_{oe}$  patch has a lower  $Z_{oe}$  value than the differential line pair on the high- $Z_{oe}$  because the  $Z_{oe}$  decreases as the distance between a differential line pair and a ground patch is reduced [18]. The via structures maintain the direct current (DC) connection between the ground patches for the low- $Z_{oe}$  and the high- $Z_{oe}$ . The ground patches below the

Fig. 1. Proposed VSI-EBG structure for suppression of CM noise in differential signaling.

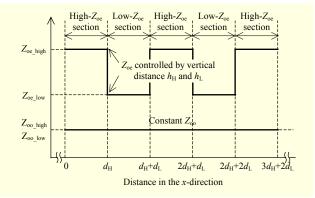

Fig. 2. Main idea of VSI-EBG structure for differential signaling, which illustrates constant odd-mode characteristic impedance, whereas periodic impedance perturbations of even-mode characteristic impedance.

differential lines are vertically distributed with the layer alternating periodically along the differential lines, which results in the repetition of the stepped impedance for the evenmode propagation. The periodic impedance perturbation produces the bandgap to mitigate the CM noise propagation through the differential line pair.

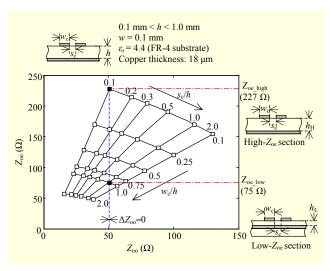

On the other hand, for the odd-mode propagation, the impedance perturbation needs to be avoided. The odd-mode characteristic impedance  $(Z_{\infty})$  needs to be constant along the differential lines so as not to degrade the differential characteristics. As shown in Fig. 2, the key feature in the design of the proposed VSI-EBG structure is forming the variations of the  $Z_{0e}$  only. The vertical distance between a differential line pair and a ground patch is denoted by h. The  $Z_{oe}$  and  $Z_{oo}$  are both determined by  $h_{\rm H}$  and  $h_{\rm L}$ , H and L denoting high and low, respectively. In Fig. 3, we present an approach to achieving the stepped impedance of  $Z_{\infty}$ , minimizing the variations of the  $Z_{\infty}$ . Figure 3 shows a  $Z_{\infty}$ - $Z_{\infty}$  diagram of the microstrip coupled lines used in the typical PCB applications. The width and spacing of the lines are denoted by  $w_c$  and  $s_c$ , respectively. The  $Z_{oe}$  and  $Z_{oo}$  are calculated using the equations in [18]. From the

Fig. 3.  $Z_{oe}$ - $Z_{oo}$  impedance diagram for design of high- and low- $Z_{oe}$  sections.

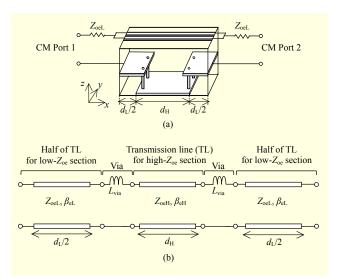

Fig. 4. (a) Unit cell of VSI-EBG structure and (b) equivalent circuit model for deriving dispersion equations.

impedance diagram, the design parameters ( $w_c$ ,  $s_c$ ,  $h_H$ ,  $h_L$ ) can be determined geometrically. Firstly, the  $Z_{\infty}$  value is determined. A vertical line at the point where  $Z_{\infty} = 52~\Omega$ , denoted by the blue dotted line in Fig. 3, is drawn. Along this line, the points of intersection can be used to determine the  $Z_{\infty}$  values for the design of the VSI-EBG structure. To achieve the wideband bandgap, the most distant  $Z_{\infty}$  values can be chosen. The reason why the most distant values can increase the stopband bandwidth will be explained clearly in section III.

## III. Dispersion Analysis

In this section, the dispersion equations of the proposed VSI-EBG structure are extracted to explain the principles of the CM noise suppression by the bandgap and investigate the design parameter effects on the bandgap. For the dispersion analysis, the unit cell of the VSI-EBG structure is defined as shown in Fig. 4(a). The equivalent circuit model of the VSI-EBG unit cell for the even-mode propagation is developed as shown in Fig. 4(b).

For the even-mode propagation, the differential line and the corresponding patch can be modeled as the transmission line. For instance, the high- $Z_{\rm oe}$  section can be represented as the transmission line having the length of  $d_{\rm H}$ , the even-mode propagation constant of  $\beta_{\rm eH}$ , and the even-mode characteristic impedance of  $Z_{\rm oeH}$ . The via structure is modeled as the via inductance  $L_{\rm via}$ . To obtain the dispersion equations, the unit cell is analyzed using the ABCD parameters, where the unit cell has the length of  $d_{\rm H}$ + $d_{\rm L}$ , the effective phase constant  $\beta_{\rm eff}$ , and the characteristic impedance  $Z_{\rm oeff}$ . The ABCD parameters are given by

$$\begin{pmatrix}

A_{\text{eff}} & B_{\text{eff}} \\

C_{\text{eff}} & D_{\text{eff}}

\end{pmatrix} = \begin{pmatrix}

A_{\text{low}} & B_{\text{low}} \\

C_{\text{low}} & D_{\text{low}}

\end{pmatrix} \begin{pmatrix}

1 & j\omega L_{\text{via}} \\

0 & 1

\end{pmatrix} \begin{pmatrix}

A_{\text{high}} & B_{\text{high}} \\

C_{\text{high}} & D_{\text{high}}

\end{pmatrix}$$

$$\times \begin{pmatrix}

1 & j\omega L_{\text{via}} \\

0 & 1

\end{pmatrix} \begin{pmatrix}

A_{\text{low}} & B_{\text{low}} \\

C_{\text{low}} & D_{\text{low}}

\end{pmatrix}, \tag{1}$$

where the equation for the  $L_{via}$  is used in [19] and ABCD parameters are given by

$$\begin{pmatrix} A_{\text{eff}} & B_{\text{eff}} \\ C_{\text{eff}} & D_{\text{eff}} \end{pmatrix}$$

$$= \begin{pmatrix} \cos\left(\beta_{\text{eff}}(d_{\text{H}} + d_{\text{L}})\right) & jZ_{\text{oeff}} \sin\left(\beta_{\text{eff}}(d_{\text{H}} + d_{\text{L}})\right) \\ \frac{j}{Z_{\text{oeff}}} \sin\left(\beta_{\text{eff}}(d_{\text{H}} + d_{\text{L}})\right) & \cos\left(\beta_{\text{eff}}(d_{\text{H}} + d_{\text{L}})\right) \end{pmatrix}, (2)$$

$$\begin{pmatrix} A_{\text{low}} & B_{\text{low}} \\ C_{\text{low}} & D_{\text{low}} \end{pmatrix} = \begin{pmatrix} \cos\left(\beta_{\text{eL}}(d_{\text{L}})/2\right) & jZ_{\text{oeL}}\sin\left(\beta_{\text{eL}}(d_{\text{L}})/2\right) \\ \frac{j}{Z_{\text{oeL}}}\sin\left(\beta_{\text{eL}}(d_{\text{L}})/2\right) & \cos\left(\beta_{\text{eL}}(d_{\text{L}})/2\right) \end{pmatrix},$$

(3)

$$\begin{pmatrix}

A_{\text{high}} & B_{\text{high}} \\

C_{\text{high}} & D_{\text{high}}

\end{pmatrix} = \begin{pmatrix}

\cos(\beta_{\text{eH}}d_{\text{H}}) & jZ_{\text{oeH}}\sin(\beta_{\text{eH}}d_{\text{H}}) \\

\frac{j}{Z_{\text{oeH}}}\sin(\beta_{\text{eH}}d_{\text{H}}) & \cos(\beta_{\text{eH}}d_{\text{H}})

\end{pmatrix}, (4)$$

$$Z_{\text{oeH(L)}} = \frac{1}{2\pi} \sqrt{\frac{\mu_{\text{o}}}{\varepsilon_{\text{eff}} \varepsilon_{\text{o}}}} \ln \left( \frac{8h_{\text{H(L)}}}{w_{\text{eff}}} + \frac{w_{\text{eff}}}{4h_{\text{H(L)}}} \right).$$

(5)

Evaluating the A component, we can obtain the dispersion equation for the analysis of the propagation characteristics and the design parameter effects on the bandgap.

$$\cos(\beta_{\text{eff}}(d_{\text{H}} + d_{\text{L}})) = \frac{1}{4} \left( 2 + \frac{Z_{\text{oeH}}}{Z_{\text{oeL}}} + \frac{Z_{\text{oeL}}}{Z_{\text{oeH}}} \right) \cos(\beta_{\text{eH}} d_{\text{H}} + \beta_{\text{eL}} d_{\text{L}})$$

$$+ \frac{1}{4} \left( 2 - \frac{Z_{\text{oeH}}}{Z_{\text{oeL}}} - \frac{Z_{\text{oeL}}}{Z_{\text{oeH}}} \right) \cos(\beta_{\text{eH}} d_{\text{H}} - \beta_{\text{eL}} d_{\text{L}})$$

$$- \frac{\omega L_{\text{via}}}{2} \left( \frac{1}{Z_{\text{oeH}}} + \frac{1}{Z_{\text{oeL}}} \right) \sin(\beta_{\text{eH}} d_{\text{H}} + \beta_{\text{eL}} d_{\text{L}})$$

$$- \frac{\omega L_{\text{via}}}{2} \left( \frac{1}{Z_{\text{oeH}}} - \frac{1}{Z_{\text{oeL}}} \right) \sin(\beta_{\text{eH}} d_{\text{H}} - \beta_{\text{eL}} d_{\text{L}})$$

$$+ \frac{(\omega L_{\text{via}})^{2}}{4Z_{\text{oeH}} Z_{\text{oeL}}} (\cos(\beta_{\text{eH}} d_{\text{H}} - \beta_{\text{eL}} d_{\text{L}}))$$

$$- \cos(\beta_{\text{eH}} d_{\text{H}} + \beta_{\text{eL}} d_{\text{L}})).$$

(6)

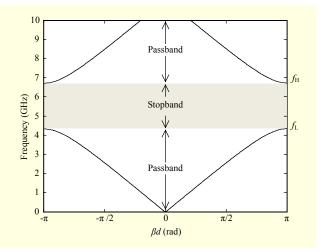

Equation (6) can be approximated by ignoring the via inductance  $L_{via}$ , which leads to removing the last three terms. They have no significant effects on the bandgap in the frequency of interest. In the paper, the  $L_{via}$  is considered as only the inductance of the shorting via structure for the sake of simplicity. However, the  $L_{via}$  is attributed to the entire physical transition from a low-Z<sub>oe</sub> ground patch to a high-Z<sub>oe</sub> ground patch. For a more exact  $L_{via}$  value, a via inductance of a return path and a mutual inductance between vias located at the same ground patch can be considered. The inductances are affected by the design parameters of the via diameter, the pitch between vias located at the same ground patch, the number of vias at the edge, and the setback distance from the center of the vias to the edge of the ground patch. To demonstrate the derived dispersion equation, the example structure is employed with the parameters  $Z_{\text{oeH}}/Z_{\text{oeL}} = 2$ ,  $L_{\text{via}} = 0$  nH,  $d_{\text{H}} = 8$  mm, and  $d_L = 8$  mm. The parameter values are determined by considering the implementation of the proposed VSI-EBG structure in the typical PCB applications. The propagation characteristic of the example VSI-EBG structure is calculated using the simplified dispersion of (6), as shown in Fig. 5. Clearly, it is found that the VSI-EBG structure forms the bandgap between the lower cutoff frequency  $(f_L)$  and the higher cutoff frequency  $(f_H)$ . It is expected that the CM noise in the bandgap of the VSI-EBG structure will be significantly suppressed, an effect experimentally verified in section IV.

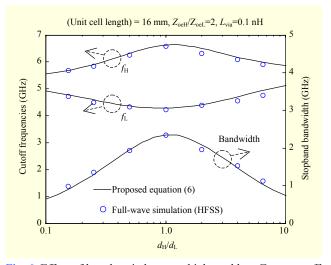

The critical design parameters  $d_{\rm H}$ ,  $d_{\rm L}$ ,  $Z_{\rm oeH}$ , and  $Z_{\rm oeL}$  are examined using the dispersion of (6). For the analysis of the length ratio ( $d_{\rm H}/d_{\rm L}$ ) effect, the example structure is considered with the following values:  $d_{\rm H}+d_{\rm L}=16$  mm,  $Z_{\rm oeH}/Z_{\rm oeL}=2$ , and  $L_{\rm via}=0.1$  nH. The effects on the  $f_{\rm L}$ ,  $f_{\rm H}$ , and stopband bandwidth are investigated with variations of  $d_{\rm H}/d_{\rm L}$  from 0.1 to 10, as shown in Fig. 6. The stopband bandwidth increases as the  $d_{\rm H}/d_{\rm L}$  value approaches 1. Consequently, the stopband bandwidth is maximized when the length of the high- and low-

Fig. 5. Dispersion diagram for VSI-EBG structure which illustrates stopband formed by periodic stepped impedance.

Fig. 6. Effect of length ratio between high- and low- $Z_{oe}$  on cutoff frequencies and stopband bandwidth.

$Z_{\text{oe}}$  sections are the same (that is,  $d_{\text{H}} = d_{\text{L}}$ ). In addition to maximizing the bandwidth, the other notable thing of the analysis results is that the considerable extension of the stopband bandwidth is achieved by both a reduction in the  $f_{\text{L}}$  and an increase in the  $f_{\text{H}}$ . A reduction in the  $f_{\text{L}}$  implies that the VSI-EBG structure that has a  $d_{\text{H}}/d_{\text{L}}$  value of 1 can have a smaller unit cell size than VSI-EBG structures that have other  $d_{\text{H}}/d_{\text{L}}$  values to achieve the same  $f_{\text{L}}$  because the  $f_{\text{L}}$  of a periodic stepped impedance structure such as the VSI-EBG structure is inversely proportional to the unit cell length [18]. It is beneficial to the bandwidth enhancement and the size reduction that the lengths of the high- and low- $Z_{\text{oe}}$  sections become equal.

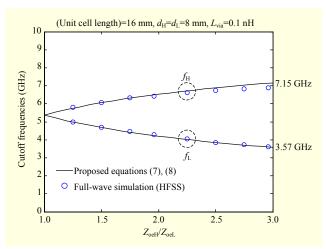

In the further analysis of the  $Z_{\text{oeH}}/Z_{\text{oeL}}$  effect, the example

Fig. 7. Effect of impedance ratio between high- and low- $Z_{oe}$  on cutoff frequencies of bandgap.

structure with  $d_{\rm H} = d_{\rm L}$  is considered due to the aforementioned analysis result. Adding the assumption of the ignorable via inductance and difference between  $\beta_{\rm eL}$  and  $\beta_{\rm eH}$ , (6) can be extracted explicitly as the closed-form expression in the following.

$$f_{\rm L} = \frac{1}{2\pi} \cdot \frac{v_{\rm p}}{2d_{\rm H}} \cos^{-1} \left( 1 - \frac{8}{2 + Z_{\rm oeH} / Z_{\rm oeL} + Z_{\rm oeL} / Z_{\rm oeH}} \right), \quad (7)$$

$$f_{\rm H} = \frac{1}{2\pi} \cdot \frac{v_{\rm p}}{2d_{\rm H}} \left( 2\pi - \cos^{-1} \left( 1 - \frac{8}{2 + Z_{\rm oeH} / Z_{\rm oeL} + Z_{\rm oeL} / Z_{\rm oeH}} \right) \right).$$

Using (7) and (8), the impedance ratio effect is investigated with the variations of the  $Z_{\text{oeH}}/Z_{\text{oeL}}$  value being from 1 to 3, as shown in Fig. 7. The monotonic increase in the  $f_{\text{H}}$  and the reduction in the  $f_{\text{L}}$  are shown as the  $Z_{\text{oeH}}/Z_{\text{oeL}}$  increases. From the analysis result, it is found that the high  $Z_{\text{oeH}}/Z_{\text{oeL}}$  value needs to be used to improve the stopband bandwidth. According to analysis results, it is predicted that the bandgap extend from 3.57 GHz to 7.15 GHz for the VSI-EBG structure with an impedance ratio value of 3. In section IV, the prediction is compared to the measurements using the VSI-EBG structure fabricated in the multilayer PCBs.

To validate (6) through (8), the results of the proposed equations are compared with the full-wave simulation results obtained using HFSS [20]. As shown in Figs. 6 and 7, the proposed equations are verified through agreement with the HFSS results.

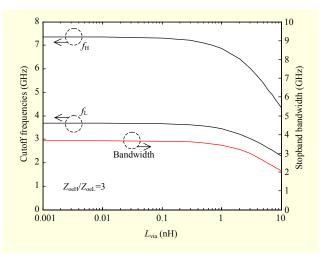

From the analysis of the impedance ratio effect in Fig. 7, it is found that the increasing difference between the  $h_{\rm H}$  and the  $h_{\rm L}$  is beneficial to the stopband enhancement. However, the improvement is limited in practical PCB applications due to the inductance of the via structure. For the considerably high value

Fig. 8. Via inductance effect on cutoff frequencies of bandgap.

of the  $h_{\rm H}$ , the via inductance becomes a significant parameter for the stopband bandwidth, and its effect cannot be ignored. In Fig. 8, the via inductance effect on the  $f_{\rm L}$  and  $f_{\rm H}$  is added. Figure 8 depicts the limitation of the stopband bandwidth imposed by the large values of the via inductance. The variations of the cutoff frequencies with regard to the change of the via inductance is obtained using the dispersion of (6). As shown in Fig. 8, the large value of the via inductance decreases in both  $f_{\rm L}$  and  $f_{\rm H}$ . However, the decreasing rate of the  $f_{\rm H}$  is faster than that of the  $f_{\rm L}$ , thus reducing the stopband bandwidth.

In summary, the effects of the main design parameters on the stopband enhancement are thoroughly investigated using the proposed dispersion equations throughout the section. As can be seen in Figs. 6 through 8, the performance of the VSI-EBG structure can be maximized by theoretical procedures and optimized for practical use in the high-speed PCBs.

## IV. Experiment Results

To verify the proposed VSI-EBG structure in suppressing wideband CM noise, two test vehicles (TVs) are fabricated using the PCB process with the through hole via structure. FR-4 ( $\varepsilon_r$  = 4.4,  $\tan\delta$  = 0.02) is used as a dielectric material. The PCB process with the through hole via structure and the FR-4 material is well known as the manufacturing process for high-speed boards that bears a low cost and possesses high manufacturing reliability. TV A is designed as a reference structure. As shown in Fig. 9(a), TV A has differential lines on the solid ground without the VSI-EBG structure. TV B has the VSI-EBG structure for differential signaling, which consists of three copper layers, as shown in Fig. 9(b). The top layer is for the differential line pair, the inner layer is for the low- $Z_{\infty}$  ground patches, and the bottom layer is for the high- $Z_{\infty}$  ground patches. The five unit cells of the VSI-EBG structure are in TV

Table 1. Design parameters and dimensions for TV A and TV B.

| Parameter        | Dimension (mm) | Parameter    | Dimension (mm) |

|------------------|----------------|--------------|----------------|

| $h_{ m H}$       | 0.9            | $S_{ m c}$   | 0.1            |

| $h_{ m L}$       | 0.1            | t            | 0.018          |

| $d_{\mathrm{H}}$ | 8.0            | $d_{ m via}$ | 0.25           |

| $d_{ m L}$       | 8.0            | $w_{\rm t}$  | 15             |

| W <sub>c</sub>   | 0.1            | -            | -              |

Fig. 9. TVs of (a) the differential line pair with solid ground plane (TVA) and (b) VSI-EBG structure (TVB).

B. The high- $Z_{\infty}$  ground patch is connected with the low- $Z_{\infty}$ patch through two shorting via structures of which spacing is 1 mm.

The detailed design parameters and dimensions are as follows:  $h_{\rm H} = 0.9$  mm,  $h_{\rm L} = 0.1$  mm,  $d_{\rm H} = 8$  mm,  $d_{\rm L} = 8$  mm,  $w_c = 0.1$  mm,  $s_c = 0.1$  mm, t = 0.018 mm (t represents copper thickness),  $d_{via} = 0.25$  mm, and  $w_t = 15$  mm ( $w_t$  represents total

Fig. 10. Measurement setup using network analyzer and microprobes for differential lines with and without VSI-EBG structure.

width). The values are determined to obtain the proper values of the  $Z_{\infty}$  and  $Z_{\infty}$  using the design technique with the  $Z_{\infty}$ - $Z_{\infty}$ impedance diagram shown in Fig. 3. The low- $Z_{\infty}$  and high- $Z_{\infty}$ values are 75  $\Omega$  and 227  $\Omega$ , respectively, while the  $Z_{00}$  value is 52  $\Omega$  with no changes along the differential lines, regardless of the vertically distributed ground patches. Using these impedance values and the dispersion equations derived herein, the  $f_L$  and  $f_H$  can be predicted with 3.57 GHz and 7.15 GHz.

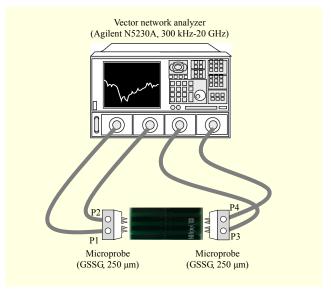

# 1. Measurements of CM Insertion Loss (S<sub>cc21</sub>)

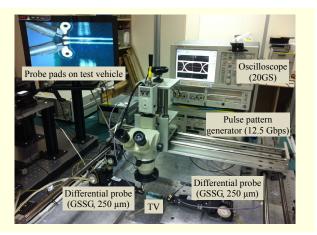

The measured CM insertion loss (S<sub>cc21</sub>) of TV A and of TV B is obtained using the four-port network analyzer with the GSSG 250 µm-pitch microprobes, as shown in Fig. 10. The use of the microprobes can minimize the parasitic effects of the additional structure for the measurement, such as the probe pads  $(0.3 \text{ mm} \times 0.3 \text{ mm})$ . The parasitic capacitance and inductance of the probe pads are small enough to be ignored in the frequency range of the interest. The single-ended scattering parameters (S-parameters) at the four ports are measured. Then, the mixed-mode S-parameters are calculated using the equations in [21] to obtain the  $S_{\infty 21}$ .

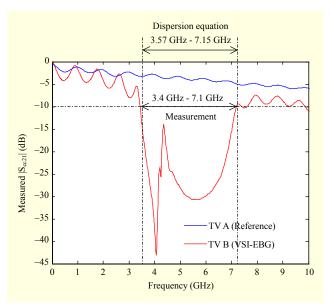

As shown in Fig. 11, the proposed VSI-EBG structure significantly suppresses the CM noise in the frequency range from 3.4 GHz to 7.1 GHz (-10 dB suppression level). The wideband suppression is achieved with the suppression bandwidth of 3.7 GHz. It is experimentally proven that the VSI-EBG structure is valuable to mitigate the CM noise in differential lines even though a backward wave propagation at 4.5 GHz, which is caused by the inductance of the via structure

Fig. 11. Measurements of CM insertion loss for TV A (differential line pair without VSI-EBG structure) and TV B (VSI-EBG structure).

and the capacitance between the high- and low- $Z_{\rm ce}$  ground patches, degrades the suppression characteristics from the bandgap. The backward wave mode can be minimized by increasing in the via diameter, which leads to reduction in the via inductance. The result of the CM noise suppression was predicted in the dispersion analysis shown in the previous section. As shown in Fig. 6, the  $f_{\rm L}$  and  $f_{\rm H}$  are estimated to be 3.57 GHz and 7.15 GHz, respectively. The estimated values from the proposed dispersion equation have desirable correlations with the measured  $S_{\rm cc21}$ .

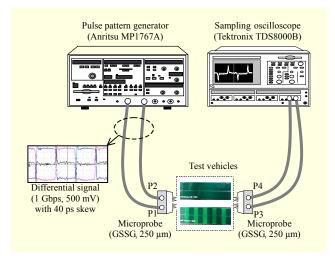

## 2. Measurements of CM Noise Suppression

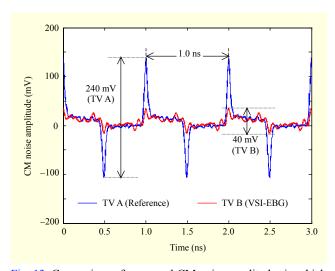

To demonstrate the CM noise suppression, the CM noise is inserted through Ports 1 and 2 of the TVs and the amplitude of CM noise at Ports 3 and 4 is measured, as shown in Fig. 12. The CM noise inserted into TVs is generated by the differential pulse trains (101010 pattern, 2 Gbps, 500 mV) with the 40 ps intra-pair skew caused by the delay line. The CM noise used here mimics the wideband noise, which can be induced by the imbalance of the length in the practical differential channels and the cables. The measured amplitude of the CM noise is defined as half of the sum of the differential pulse trains at Ports 3 and 4, acquired using a sampling oscilloscope (Tektronix, TDS 8000B).

In Fig. 13, the experiment results demonstrate that the amplitude of the CM noise voltage is significantly reduced by the VSI-EBG structure (TV B), from 240 mV to 40 mV, notable compared to the differential line pair without the VSI-

Fig. 12. Measurement setup to demonstrate wideband suppression of CM noise caused by unbalanced differential channel.

Fig. 13. Comparison of measured CM noise amplitudes in which CM noise is significantly reduced by VSI-EBG structure.

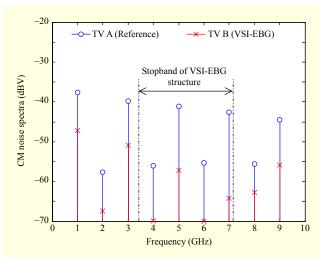

EBG structure (TV A). An 83% reduction in the peak-to-peak voltage of CM noise is achieved. Through the frequency spectrum, the significant mitigation of the CM noise can be clearly explained. In Fig. 14, the CM noise spectra for TV A and TV B are obtained using the fast Fourier transform (FFT) of the measured CM noise voltage. In the FFT result for TV A, a significant amount of the noise harmonics can be shown. The fundamental frequency of the CM noise is 1 GHz, associated with the CM noise period of 1 ns, shown in Fig. 13. For TV A, the spectra of the CM noise extend in the wideband frequency range. On the other hand, it is shown that the noise harmonics are suppressed over the wideband frequency range for TV B. Particularly, the noise harmonics from 4 GHz to 7 GHz are considerably mitigated by the bandgap of the VSI-EBG

Fig. 14. CM noise spectra for TV A and TV B which shows wideband suppression of CM noise of VSI-EBG structure.

structure. The relatively low suppression of the noise harmonics at 5 GHz is due to the anti-resonant peak, as mentioned in Fig. 11. However, the suppression characteristics of the CM noise voltage are not significantly affected by the resonant peak because the resonant peak can influence only a single harmonic and the suppression level is still more than 10 dB. It is experimentally verified that the wideband suppression of the CM noise using the VSI-EBG structure can be achieved in the multilayer PCBs, which ensures low cost, high manufacturing reliability, and high design flexibility.

# 3. Measurements of Differential Characteristics

In the previous section, the CM characteristics of the VSI-EBG structure are thoroughly examined through the experiment results. In this section, we will explore the differential characteristics of the VSI-EBG structure through measurements of the differential-mode insertion loss ( $S_{dd21}$ ) and the eye diagram. Firstly, the measurement setup and the experiment results for the  $S_{dd21}$  will be discussed. The measurement setup for  $S_{dd21}$  is the same as the aforementioned measurement setup for  $S_{cc21}$ . From the measured S-parameters at four single-ended ports, the  $S_{dd21}$  can be calculated using the mixed-mode S-parameters [21].

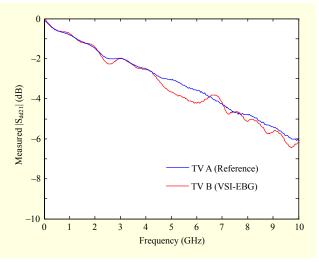

The measured  $S_{dd21}$  of TV B (VSI-EBG structure) is compared to the measurement of TV A (reference), as shown in Fig. 15. TV B has no significant degradation of the  $S_{dd21}$  except in the frequency range from 5 GHz to 6 GHz. In this frequency region, the difference in the  $S_{dd21}$  between TV A and TV B is less than 0.7 dB on average. The amount of  $S_{dd21}$  degradation is so small and its bandwidth is relatively narrow compared to the frequency spectra of high-speed differential

Fig. 15. Measurements of differential insertion loss for TV A and TV B.

Fig. 16. Photograph of measurement setup to verify differential characteristics of VSI-EBG structure.

data. Accordingly, no significant deterioration of the differential characteristics for TV B can be expected.

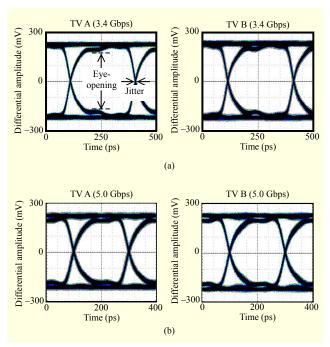

To demonstrate the differential signal integrity (SI) performance of TV B, another measurement for the eye diagram in the time domain is conducted. As shown in Fig. 16, the high-speed differential data launched from the pulse pattern generator is inserted into the TVs, and the eye diagram is measured using the sampling oscilloscope. The non-return to zero data pattern with a 2<sup>7</sup>–1 pseudorandom bit sequence is used. The measurements are performed for the two cases of the data rates, namely 3.4 Gbps and 5.0 Gbps. The data rates are adopted, considering the application of the HDMI and USB 3.0. Note that the modulation and the coding technique for the HDMI and USB 3.0 are excluded in the measurement setup.

The experiment results of the eye diagram are compared in Fig. 17, and the eye opening voltage and the peak-to-peak jitter

Fig. 17. Measurements of eye diagram for differential data with (a) 3.4 Gbps and (b) 5.0 Gbps.

are summarized in Table 2. For both data rates of 3.4 Gbps and 5.0 Gbps, the eye diagrams of TV B perform better than the eye diagrams of TV A. As shown in Table 2, it is proven that the differential characteristics of TV B are not degraded compared to TV A in terms of the eye opening voltage and the peak-to-peak jitter.

Summarizing the results in this section, it is experimentally verified that the application of the VSI-EBG structure to the high-speed differential signals in the multilayer PCBs can achieve the wideband suppression of the CM noise induced by the imbalance of the differential channels. Further, it is not necessary to sacrifice the differential SI performance. Even though it requires the multilayer and the via structures, the VSI-EBG structure can be a valuable alternative to handle CM noise in high-speed PCBs, providing wideband CM noise suppression at a low cost and with high design flexibility.

# V. Conclusion

We presented the application of the VSI-EBG structure to differential signaling for wideband CM noise suppression in the GHz frequency range. To analyze the proposed EBG structure for differential signaling, a dispersion equation was derived herein, which allowed for easy prediction of the bandgap and intuition of the design parameter effects. The performance of the proposed structure was experimentally verified for one differential line pair. However, the proposed structure can easily be extended to a few differential line pairs

Table 2. Summary of measured eye opening voltages and peak-to-peak jitters for TV A (reference) and TV B (VSI-EBG).

|                             | Data rate: 3.4 Gbps |     | Data rate: 5.0 Gbps |     |

|-----------------------------|---------------------|-----|---------------------|-----|

|                             | TV A                | TVB | TV A                | TVB |

| Eye opening voltage (mV)    | 343                 | 354 | 343                 | 354 |

| Peak-to-peak<br>jitter (ps) | 14                  | 14  | 15                  | 16  |

for multichannel applications because the idea of the VSI-EBG structure is not dedicated to a single differential line pair. For further study, the crosstalk among differential line pairs as well as the noise suppression must be considered. The use of slotted patches or high dielectric constant material can be considered for the size reduction. The miniaturized VSI-EBG structure can apply to consumer electronics with a small form factor, such as mobile phones, tablet devices, and so on.

## Acknowledgment

The authors would like to thank the anonymous reviewers for their constructive and valuable comments.

#### References

- [1] F. Jun et al., "Signal Integrity Design for High-Speed Digital Circuits: Progress and Directions," *IEEE Trans. Electromagn. Compat.*, vol. 52, no. 2, May 2010, pp. 392-400.

- [2] G. Shiue et al., "Noise Reduction Using Compensation Capacitance for Bend Discontinuities of Differential Transmission Lines," *IEEE Trans. Adv. Packag.*, vol. 29, no. 3, Aug. 2006, pp. 560-569.

- [3] J. Poltz, J. Beckett, and M. Josefsson, "Measurement and Simulation of Differential Skew in Twisted Pair Cables," *Proc.* 55th Int. Wire Cable Symp., Providence, RI, USA, Nov. 12-15, 2006, pp. 141-146.

- [4] C. Sreerama, "Effects of Skew on EMI for HDMI Connectors and Cables," *Proc. IEEE Int. Symp. Electromagn. Compat.*, vol. 2, Aug. 2006, pp. 452-455.

- [5] B. Archambeault, J.C. Diepenbrock, and S. Connor, "EMI Emissions from Mismatches in High Speed Differential Signal Traces and Cables," *IEEE Int. Symp. Electromagn. Compat.*, July, 2007, pp. 1-6.

- [6] T.-L. Wu et al., "A Novel Wideband Common-Mode Suppression Filter for Gigahertz Differential Signals Using Coupled Patterned Ground Structure," *IEEE Trans. Microw. Theory Tech.*, vol. 57, no. 4, Apr. 2009, pp. 848-855.

- [7] W.-T. Liu et al., "An Embedded Common-Mode Suppression

- Filter for GHz Differential Signals Using Periodic Defected Ground Plane," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 4, Apr. 2008, pp. 248-250.

- [8] D. Sievenpiper et al., "High-Impedance Electromagnetic Surfaces with a Forbidden Frequency Band," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 11, Nov. 1999, pp. 2059-2074.

- [9] R. Abhari and G.V. Eleftheriades, "Suppression of the Parallel-Plate Noise in High-Speed Circuits Using a Metallic Electromagnetic Band-Gap Structure," *IEEE MTT-S Int. Microw. Symp. Dig.*, June 2002, pp. 493-496.

- [10] J. Choi et al., "Noise Isolation in Mixed-Signal Systems Using Alternating Impedance Electromagnetic Bandgap (AI-EBG) Structure-Based Power Distribution Network (PDN)," *IEEE Trans. Adv. Packag.*, vol. 33, no. 1, Feb. 2010, pp. 2-12.

- [11] J. Park et al., "Double-Stacked EBG Structure for Wideband Suppression of Simultaneous Switching Noise in LTCC-Based SiP Applications," *IEEE Microw. Wireless Compon. Lett.*, vol. 16, no. 9, Sept. 2006, pp. 481-483.

- [12] M. Kim et al., "Vertical Inductive Bridge EBG (VIB-EBG) Structure With Size Reduction and Stopband Enhancement for Wideband SSN Suppression," *IEEE Microw. Wireless Compon. Lett.*, vol. 22, no. 8, Aug. 2012, pp. 403-405.

- [13] M. Kim et al., "A Compact and Wideband Electromagnetic Bandgap Structure Using a Defected Ground Structure for Power/Ground Noise Suppression in Multilayer Packages and PCBs," *IEEE Trans. Electromagn. Compat.*, vol. 54, no. 3, June 2012, pp. 689-695.

- [14] F. de Paulis et al., "Design of a Common Mode Filter by Using Planar Electromagnetic Bandgap Structures," *IEEE Trans. Adv. Packag.*, vol. 33, no. 4, Nov. 2010, pp. 994-1002.

- [15] M.H. Nisanci et al., "Optimum Geometrical Parameters for the EBG-Based Common Mode Filter Design," *Proc. IEEE Int. Symp. Electromagn. Compat.*, Aug. 2012, pp. 526-531.

- [16] C.-H. Tsai and T.-L. Wu, "A Broadband and Miniaturized Common-Mode Filter for Gigahertz Differential Signals Based on Negative-Permittivity Metamaterials," *IEEE Trans. Microw. Theory Tech.*, vol. 58, no. 1, Jan. 2010, pp. 195-202.

- [17] M. Kim et al., "Vertical Stepped Impedance EBG (VSI-EBG) Structure for Wideband Suppression of Simultaneous Switching Noise in Multilayer PCBs," *IEEE Trans. Electromagn. Compat.*, vol. 55, no. 2, Apr. 2013, pp. 307-314.

- [18] R. Ludwig, RF Circuit Design Theory and Applications, Englewood Cliffs, NJ: Prentice-Hall, 2000.

- [19] C.-L. Wang et al., "A Systematic Design to Suppress Wideband Ground Bounce Noise in High-Speed Circuits by Electromagnetic-Bandgap-Enhanced Split Powers," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 12, Dec. 2006, pp. 4209-4217.

- [20] ANSYS, Inc., High Frequency Structure Simulator (HFSS). http://www.ansys.com

- [21] W. Fan et al., "Mixed-Mode S-Parameter Characterization of

Differential Structures," *Proc. IEEE 11th Conf. Electron Packag. Technol. Conf.*, Dec. 10-12, 2003, pp. 533-537.

Myunghoi Kim received his BS, MS, and PhD in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Rep. of Korea, in 2003, 2005, and 2012, respectively. He is currently a senior member of the engineering staff at ETRI, Daejeon, Rep. of Korea. His responsibility

includes electromagnetic compatibility and RF interference for the spacecraft and the satellite systems. From 2005 to 2008, he was a researcher for signal integrity and EMC analysis of the missile electronic systems in the Agency for Defense Development (ADD), Daejeon, Rep. of Korea. He was a visiting researcher at Silicon Image, Inc., Sunnyvale, CA, USA, in 2011. He has authored or co-authored more than 30 technical papers published in refereed journals or conference proceedings on the topics of modeling, design, and measurement of SI/PI analysis and electromagnetic bandgap (EBG) structure.

Sukjin Kim received his BS in electrical and electronics engineering from Korea University, Seoul, Rep. of Korea. He then advanced to Seoul National University, Seoul, Rep. of Korea, where he received his MS in electrical engineering. He is currently pursuing his PhD in electrical engineering from the Korea Advanced

Institute of Science and Technology, Daejeon, Rep. of Korea. His current research interests include chip-package printed circuit board wireless power transfer co-design and co-simulation.

**Bumhee Bae** received his BS and MS in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Rep. of Korea, in 2009 and 2011, respectively. He is currently pursuing his PhD in electrical engineering from KAIST. His current research interest is the PI/SI/EMC of mixed-

mode systems with chip-package PCB hierarchical structures.

Jonghyun Cho received his BS, MS, and PhD in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Rep. of Korea, in 2008, 2010, and 2013, respectively. He is currently working at KAIST as a postdoctoral researcher. His current research interest is electrical design

in 2.5D and 3D IC. He is a specialist in noise coupling analysis and reduction in TSV-based 3D IC.

Joungho Kim received his BS and MS in electrical engineering from Seoul National University, Seoul, Rep. of Korea, in 1984 and 1986, respectively, and his PhD in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 1993. In 1994, he joined the Memory Division of Samsung

Electronics, where he was engaged in Gbit-scale DRAM design. In 1996, he moved to the Korea Advanced Institute of Science and Technology (KAIST). He is currently the Electrical Engineering Department chair at KAIST. Also, he is the director of the 3DIC Research Center (3DIC-RC), supported by Hynix Inc., and the Smart Automotive Electronics Research Center (SAE-RC), supported by KET Inc. He has authored or co-authored over 370 technical papers published in refereed journals or conference proceedings on the topics of modeling, design, and measurement of 3D IC, SiP, PCB, and wireless power transfer. Also, he has given more than 174 invited talks and tutorials at academic institutes and industry venues.

Jaehoon Kim received his PhD in computer engineering from Chungbuk National University, Cheongju, Rep. of Korea, in 2001. He joined ETRI in 1983, where he was involved in developing the Intelligent Network and KOREASAT projects. From 1992 to 1994, he was an OJT engineer at Martra-Marconi

Space in the UK for the KOREASAT Project. From 1995 to 1999, he participated in the KOMPSAT-1 Ground Mission Control project as a principle member of the engineering staff in system engineering. From 2000 to 2012, he participated in the KOMPSAT-2, the COMS-1, the KOMPSAT-3, and the KOMPSAT-5 Ground Mission Control projects as the team leader. His research interests are security in satellite communications, fault diagnosis of satellites using AI technologies, and satellite navigation technologies.

**Do Seob Ahn** received his BS and MS in electronics engineering from Kyungpook National University in 1988 and 1990, respectively, and his PhD in radio science and engineering from Chungnam National University in 2010. He has worked for ETRI, Daejeon, Rep. of Korea, since 1990. He is

currently the director of the Satellite Wireless Convergence Research Division of ETRI, working in the area of satellite wireless communication.