# A Single Transistor-Level Direct-Conversion Mixer for Low-Voltage Low-Power Multi-band Radios

Byoung Gun Choi, Seok-Bong Hyun, Geum-Young Tak, Hee-Tae Lee, Seong-Su Park, and Chul Soon Park

A CMOS direct-conversion mixer with a single transistor-level topology is proposed in this paper. Since the single transistor-level topology needs smaller supply voltage than the conventional Gilbert-cell topology, the proposed mixer structure is suitable for a low power and highly integrated RF system-on-a-chip (SoC). The proposed direct-conversion mixer is designed for the multi-band ultra-wideband (UWB) system covering from 3 to 7 GHz. The conversion gain and input P1dB of the mixer are about 3 dB and -10 dBm, respectively, with multi-band RF signals. The mixer consumes 4.3 mA under a 1.8 V supply voltage.

Keywords: Direct-conversion mixer, single transistorlevel topology, RF CMOS, wireless SoC, UWB.

# I. Introduction

The ongoing very-large-scale integration (VLSI) technology down-scaling toward deep submicron processes yields many advantages and challenges in developing a system-on-a-chip (SoC) that includes RF and analog circuits. A key problem for the implementation of RF SoC is the reduction of supply voltage, even sub-volt supplies ( $V_{DD} < 1V$ ), as the design rules of the CMOS device are scaled down to and beyond 90 nm [1]. Since the supply voltage determines the maximum voltage swing level, decreasing the supply voltage means decreasing the maximum achievable signal level, which degrades the RF performances such as linearity and dynamic range. On the other hand, linearity requirements have become more stringent as recent wireless systems have adopted multi-standards and broadband characteristics. Short-range high-speed wireless systems such as an ultra-wideband (UWB) wireless personal area network (WPAN) [2] require low-power, low-cost, and linear RF transceivers. Such wideband systems do not occupy the frequency band exclusively and cannot use high-Q bandpass filters, so large in-band interference tones exist in the input of the receiver chips. High linearity is thus required to prevent intermodulation and de-sensitization problems.

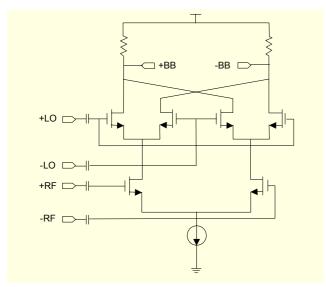

Active mixers, commonly used for frequency conversion in most wireless communication systems, determine the linearity of the RF receiver. While conventional mixers use Gilbert-cell topology as shown in Fig. 1 for multi-mode applications [3], it has potential linearity problems due to the number (two or three) of stacked transistors with a cascode structure. As the supply voltage becomes lower and lower, it is more difficult to get bias conditions and a sufficient level of voltage swing under a restricted supply voltage. There are some other mixers

Manuscript received Jan. 12, 2005; revised May 25, 2005.

The material in this work was presented in part at IT-SoC 2004, Seoul, Korea, Oct. 2004.

Byoung Gun Choi (phone: +82 42 860 1797, email: cbgun@etri.re.kr), Seok-Bong Hyun (email: sbhyun@etri.re.kr), Geum-Young Tak (email: gytak@etri.re.kr), Hee-Tae Lee (email: htlee@etri.re.kr), and Seong-Su Park (email: sspark@etri.re.kr) are with Basic Research Laboratory ETRI Daeieon Korea

Chul Soon Park (email: parkcs@icu.ac.kr) is with the School of Engineering, ICU, Daejeon, Korea.

suitable for low-voltage operation [4], [5], but some features such as bandwidth and/or conversion gain are not suitable for high-speed multi-band systems.

In this paper, we propose a low-voltage wideband mixer topology suitable for the current and near future mixed signal SoC technology. The rest of this paper is organized as follows. The circuit topology and the basic operation principle of the proposed mixer are explained in section II. Section III presents the circuit details for a specific system, a multi-band direct-conversion receiver. Section IV shows the simulation and experimental results, followed by our conclusions in section V.

Fig. 1. Conventional Gilbert-cell mixer.

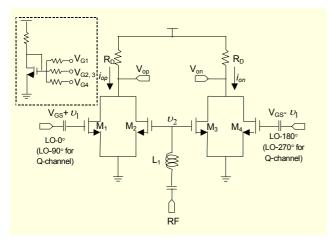

Fig. 2. A schematic diagram of the single-level direct-conversion mixer.

# II. Operation Principle

The proposed low-voltage direct-conversion mixer is composed of two drain-coupled NMOS pairs. A simplified

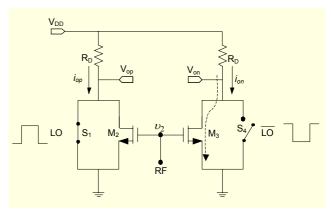

schematic diagram of the mixer is shown in Fig. 2. A single-ended RF signal is applied to the gate terminals of  $M_2$  and  $M_3$ , and relatively high powered differential LO signals are applied to the gate terminals of  $M_1$  and  $M_4$ . Mixing between RF and LO signals occurs at the drain-coupled transistor pairs ( $M_1$ - $M_2$  and  $M_3$ - $M_4$ ). The transistors  $M_2$  and  $M_3$  act as transconductance stages, and  $M_1$  and  $M_4$  act as switches. For a simplified explanation, we can model  $M_1$  and  $M_4$  as switches driven by the logic signals LO and  $\overline{LO}$  as shown in Fig. 3.

Fig. 3. Simplified functional representation of the proposed mixer for a large LO signal.

The signal,  $v_1$ , the AC component of the gate terminal of  $M_1$  in Fig. 2, can be considered as the logic signal LO in Fig. 3. If LO is positive, switch  $S_1$  in the left side is turned on, and the drain of  $M_2$  is connected to the source. Thus, the current at the positive output terminal,  $i_{op}$ , due to the RF signal  $v_2$  is very small. On the other hand, switch  $S_4$  in the right side is turned off, and most of the output current,  $i_{on}$ , is the drain current of  $M_3$ . The overall differential output current thus becomes

$$i_o = i_{op} - i_{on} = -i_{d.M_2} = -(-g_{m3} \cdot v_2), \quad \text{if } v_1 > 0.$$

(1)

When LO signal  $v_1$  is negative,  $S_1$  is turned off and  $S_4$  is on. In this case,  $M_2$  is active and  $M_3$  is in the triode region.

$$i_o = i_{op} - i_{on} = i_{d.M.} = -g_{m2} \cdot v_2, \quad \text{if } v_1 < 0.$$

(2)

Thus, the sign of the overall differential output current is determined by the sign of LO, and the output signal is

$$i_o = g_{m2} \cdot \nu_2 \cdot \operatorname{sgn}(\nu_1) . \tag{3}$$

If the LO signal is periodic with frequency  $f_{LO}$ , the sgn  $(v_1)$  term becomes a periodic square wave function. Fourier series expansion gives

$$i_o = g_{m2} \cdot \sin(\omega_2 t) \cdot \frac{\pi}{4} \left( \sin \omega_1 t - \frac{1}{3} \sin 3\omega_1 t + \frac{1}{5} \sin 5\omega_1 t - \cdots \right). (4)$$

This expression is the same as that of the traditional single-balanced active mixer. Since higher harmonic terms are easily removed by low pass filters connected to the output of the mixer, we can obtain the frequency conversion component. While a single-balanced mixer may suffer from a high DC offset problem, the proposed mixer doesn't care about the problem because the multi-band UWB system has no subcarrier near DC (DC to 4.125 MHz). A simple AC-coupling capacitor can be used for eliminating a DC term.

# III. Circuit Design

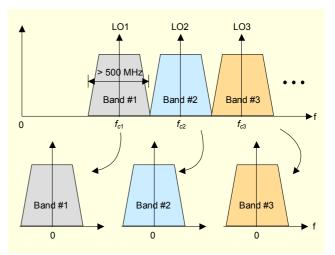

The proposed direct-conversion mixer is designed for the multi-band system covering from 3 to 7 GHz. Each RF signal band has a bandwidth of over 500 MHz, and the multiple LO signals are used for direct down converting the corresponding bands of RF signals. Each LO frequency is the same value as the center frequency of the RF signal for direct-conversion. Table 1 lists the band plan for the multi-band system of this work, and Fig. 4 depicts the proposed frequency allocation of the multi-band direct-conversion receiver.

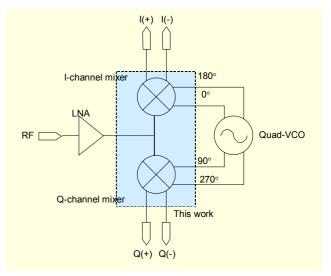

A block diagram of the direct-conversion receiver including the proposed mixers is shown in Fig. 5. The output signal of a single-ended low-noise amplifier enters into both the I-channel and Q-channel mixers. The I-channel mixer receives a single-ended RF signal and differential LO signals, having 0° and 180° phases from the output of the quadrature voltage-controlled oscillator for generating the differential in-phase baseband signals. The Q-channel mixer receives the same single-ended RF signal and 90° shifted differential LO signals, having 90° and 270° phases for differential quadrature baseband signals.

The mixer topology has a single transistor-level structure. The single transistor-level mixer has several advantages compared to the conventional two or three-level stacked Gilbert-cell mixers, whose topology is shown in Fig. 1. Because the single transistor-level mixer needs a smaller supply voltage than the conventional mixers, it can reduce DC

Table 1. Band plan for the multi-band high-rate WPAN system.

| Band ID | Center frequency, $f_c$ (MHz) | Bandwidth (MHz) | LO frequency<br>(MHz) |                 |

|---------|-------------------------------|-----------------|-----------------------|-----------------|

| #1      | 3432                          | > 500           | 3432 (LO1)            | This work       |

| #2      | 3960                          |                 | 3960 (LO2)            |                 |

| #3      | 4488                          |                 | 4488 (LO3)            |                 |

| #4      | 5016                          |                 | 5016(LO4)             | Further<br>work |

| #5      | 5808                          |                 | 5808(LO5)             |                 |

| #6      | 6336                          |                 | 6336(LO6)             |                 |

Fig. 4. Frequency plan of the RF receiver for the multi-band WPAN system.

Fig. 5. A block diagram of the direct-conversion receiver including the proposed mixers for a multi-band UWB system.

power consumption. It can also be integrated with analog and digital circuits sharing the same low supply voltage, which is desirable for a mixed signal SoC. The on-chip spiral inductor  $L_1$  in Fig. 2 is used for wideband input impedance matching for three different RF frequency bands. Because the maximum available gain of a CMOS decreases as frequency increases, the matched impedance point for an RF input port was intentionally selected at a higher frequency range for the purpose of the flat gain-bandwidth characteristic of a UWB system.

### IV. Performances of the Mixer

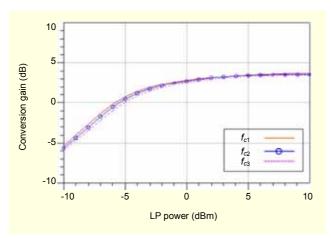

The direct-conversion mixer was designed with 0.18 µm CMOS technology. Fixing the baseband frequency to 100 MHz,

simulated gain variations of the mixer in three RF bands as a function of LO power are shown in Fig. 6. Each conversion gain of the three RF bands increases as LO power increases from -10 to 10 dBm. The conversion gains at  $P_{LO} = 0$  dBm are 2.5, 2.7, and 2.8 dB with the center frequencies of the three RF bands at 3.432 ( $f_{c1}$ ), 3.96 ( $f_{c2}$ ), and 4.488 GHz ( $f_{c3}$ ), respectively.

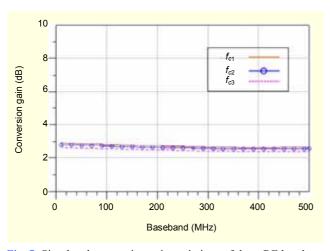

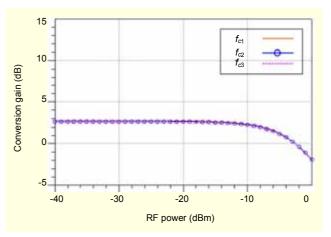

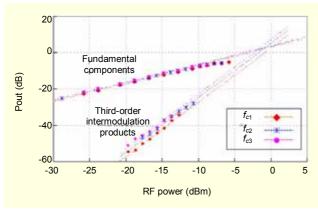

The wideband characteristics of the mixer and conversion gain as a function of RF power are simulated; Figs. 7 and 8 show the results. The curves show that the input P1dBs of the three bands are about -7 dBm.

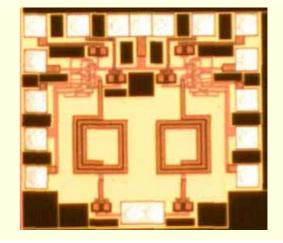

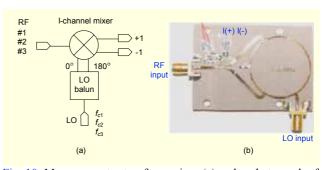

A photograph of fabricated RF integrated circuit mixers is shown in Fig. 9. The chip size is  $0.9 \text{ mm} \times 0.8 \text{ mm}$ . The performance of the mixer was characterized with an evaluation test circuit board for a single transistor-level mixer. A block diagram of the test setup and a photograph of the PCB are shown in Fig. 10. The PCB baluns, with center frequencies at

Fig. 6. Simulated conversion gain variations of three RF bands as a function of LO power ( $f_{BB}$ =100 MHz,  $P_{RF}$ = -30 dBm).

Fig. 7. Simulated conversion gain variations of three RF bands as a function of the bandwidth of the baseband ( $P_{LO}$ = 0 dBm,  $P_{RF}$ = -30 dBm).

$f_{cl}$ ,  $f_{c2}$ , and  $f_{c3}$ , were designed to make differential LO signals from each single-ended LO signal.

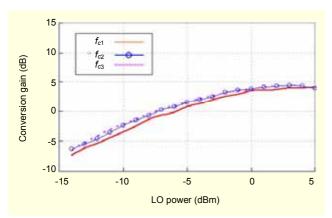

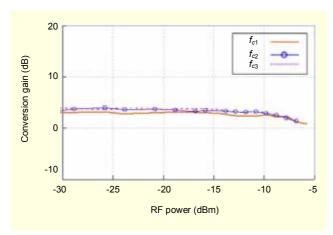

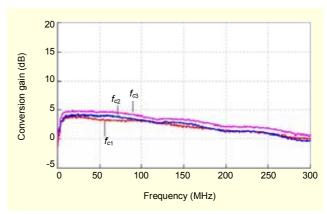

Measured conversion gains versus LO power and RF power are shown in Figs, 11 and 12, respectively. With a fixed LO power at 0 dBm, the conversion gain of each RF band is about 3 dB and the input P1dB is around -10 dBm. The measured

Fig. 8. Simulated conversion gain as a function of RF power ( $P_{LO}$ = 0 dBm,  $f_{BB}$ = 100 MHz).

Fig. 9. Photograph of the fabricated mixers.

Fig. 10. Measurement setup for a mixer (a) and a photograph of the PCB (b).

IP3s of the mixer at 100 MHz of baseband frequency corresponding to three RF input signals are shown in Fig. 13. The IIP3 of a mixer varies from 0 to -2 dBm with increasing the center frequency of the RF signals from  $f_{cl}$  to  $f_{c3}$ . Also, the

Fig. 11. Measured conversion gain variations of three RF bands as a function of LO power ( $f_{BB}$ = 100 MHz,  $P_{RF}$ = -30 dBm).

Fig. 12. Measured conversion gain as a function of RF power  $(P_{LO}=0 \text{ dBm}, f_{BB}=100 \text{ MHz}).$

Fig. 13. The IP3s of the propsed direct-conversion mixer ( $P_{LO}$ = 0 dBm,  $f_{BB}$ = 100 MHz).

Fig. 14. Conversion gain variations as a function of baseband frequency.

Table 2. The performances of the proposed mixer and a comparison with other low voltage mixers.

| Parameters           | This work            | [4]              | [5] <sup>1)</sup> | [6]          |

|----------------------|----------------------|------------------|-------------------|--------------|

| Topology             | Source/Drain coupled | Folded<br>mirror | Folded<br>mixer   | Gilbert-cell |

| RF frequency (GHz)   | 3 - 5                | 0.9              | 0.9               | 1.9          |

| # of Tr. stack       | 1                    | 2                | 2                 | 3            |

| Supply voltage (V)   | 1.8                  | 1.8              | 1.25              | 1.8          |

| Conversion gain (dB) | ~3                   | 2.5              | -6.5              | 0.5          |

| Input IP3 (dBm)      | >-2                  | 1                | 15                | -6           |

| Current (mA/mixer)   | 4.3                  | 5                | 3                 | 4.8          |

<sup>1)</sup> Simulated results

conversion gain variation with baseband frequency is shown in Fig. 14. Table 2 compares the performances of the proposed drain-coupled down-conversion mixer with those of the previous works for low voltage operation. The previously reported mixers have at least a two-transistor stacked topology, and this might restrict the gain under a low supply voltage.

### V. Conclusion

A novel direct-conversion mixer with a single transistor-level topology is presented in this paper. The single transistor-level mixer structure can be operated under a much smaller supply voltage compared to the conventional two or three-level stacked Gilbert-cell mixers, which is suitable for the low power and highly integrated RF SoC. Experimental results of the proposed direct-conversion mixer show good agreement with the simulation results for multi-band operation in a 3 to 5 GHz range. The conversion gain and input P1dB of the mixer are about 3 dB and -10 dBm, respectively, with the multi-band RF signals.

### References

- [1] Semiconductor Industry Association, *International Technology Roadmap for Semiconductors*, *Overall Roadmap Technology Characteristics*, 2003, pp. 56-57.

- [2] Anuj Batra, "Multi-band OFDM Physical Layer Proposal," *IEEE* 802.15-03/267r2, July 14, 2003, pp. 14-17.

- [3] Seok-Bong Hyun, Geum-Young Tak, Sun-Hee Kim, Byung-Jo Kim, and Seong-Su Park, "A Dual-Mode 2.4-GHz CMOS Transceiver for High-Rate Bluetooth Systems," *ETRI J.*, vol. 26, no. 3, June 2004, pp. 229-240.

- [4] W.-C. Cheng, C.-F. Chan. C.-S. Choy, and K-P. Pun, "A 1.5 V 900 MHz CMOS Current Folded-Mirror Mixer," *Proc. ASIC* 2003, vol. 2, Oct. 2003, pp. 21-24.

- [5] M-S. Yang, H-R. Kim, and S-G. Lee, "A 900MHz Low Voltage Low Power Highly Linear Mixer for Direct-Conversion Receivers," *Proc. ICECS 2003*, vol. 3, 2003, pp. 14-17.

- [6] P. J. Sullivan, B. A. Xavier, and W. H. Ku, "Low Voltage Performance of a Microwave CMOS Gilbert Cell Mixer," *IEEE J. of Solid-State Circuits*, vol. 32, no. 7, 1997, pp. 1151-1155.

**Byoung Gun Choi** received the BS degree in electronic engineering from Yeungnam University in 1995 and the MS and PhD degrees from Information and Communications University (ICU) in 2000 and 2005. He was with Samsung Electronics as a process engineer from August 1995 to October 1996. Since 2005,

he has been with Electronics and Telecommunications Research Institute (ETRI), Daejeon, Korea, as a Senior Member of Engineering Staff. His research interests include design of low power and low-voltage RFICs and SoCs for high speed wireless communications.

Seok-Bong Hyun received the BS, MS, and PhD degrees in physics from Korea Advanced Institute of Science and Technology (KAIST) in 1991, 1993, and 1998. He was with the Electrical Engineering Department, KAIST, as a Post Doctorial Research Fellow from March 1998 to June 1999. In 1999 he joined ETRI

where he has been involved in the design of RF and analog integrated circuits for short-range wireless communication systems and Bluetooth. His research interests include the design of mixed signal ICs and very high speed wireless network systems.

communication ICs.

Hee-Tae Lee received the BS in electrical engineering from National Central Vocational Training Institute in 1978. He joined ETRI in 1981 and has worked in CMOS RFIC design on short-range wireless communication modules. Currently, he is working in CMOS analog circuits and communication IC

Geum-Young Tak received the BS and MS degrees in electrical engineering from Seoul

National University, Korea, in 2000 and 2002.

Since he joined ETRI in 2002, he has been

involved in CMOS RFIC design for short-range

wireless communication modules. His research

interests include CMOS analog circuits and

packaging.

Seong-Su Park received the BS degree in metallurgy from Yonsei University, Korea, in 1984, and the MS and PhD degrees in materials science from KAIST, Korea, in 1986 and 1992. In 1993, he joined ETRI where he is now a Team Manager. Until 1998, his research area was in MMICs and high speed optical devices

packaging such as 5 GHz amplifier modules, 10 Gbps laser diode modules, and others. Since 1999, he has been in charge of the development of Bluetooth chips.

Chul Soon Park received the BS degree in metallurgical engineering from Seoul National University, Seoul Korea in 1980, and the MS and PhD degrees in materials science from KAIST in 1982 and 1985. After he joined ETRI in 1985, he was involved in the development of semiconductor devices and

circuits. Between 1987 and 1989, he studied on the initial growth of group IV semiconductors during a visit to AT&T Bell Laboratories at Murray Hill, USA. Since 1989, he has been involved in the development of compound semiconductor devices and their application to microwave and high-speed integrated circuits as a principal investigator in ETRI. Currently he is an Associate Professor of the IT Engineering School in Information and Communications University (ICU).