## UWB 응용을 위한 고주파 CMOS VCO 설계 및 제작

# A Design on High Frequency CMOS VCO for UWB Applications

박 봉 혁ㆍ이 승 식ㆍ최 상 성

Bong-Hyuk Park · Seung-Sik Lee · Sang-Sung Choi

유 약

본 논문에서는 CMOS  $0.18~\mu m$  공정을 이용하여 DS-CDMA UWB용 고주파 VCO를 설계하고 제작하였다. 위상 잡음 특성을 좋게 하기 위해서 PMOS, NMOS 소자를 대칭으로 구성한 complementary cross-coupled LC 발진 기 구조로 설계하였고, varactor를 이용하여 주파수를 조정하였다. 또한 전류원의 1/f 잡음 신호를 줄이기 위해 저항을 이용하여 전류원을 구성하였다. 스펙트럼 분석기를 이용한 측정을 위해 칩 내부에 고속 동작을 위한 인버터 버퍼를 추가로 설계하였다. 제작한 VCO의 core size는  $340~\mu m \times 535~\mu m$ 이고, 측정한 VCO의 위상 잡음은 1-MHz offset에서 -107~dBc/Hz의 특성을 나타내고, 주파수 조정 범위는  $7.09 \sim 7.52~GHz$ 의 특성을 보인다. Harmonic suppression은 32~dB, VCO core의 전류 소모는 1.8~V~S급 전압에서 2~mA의 저전력 소모를 나타내도록 설계하였다.

#### **Abstract**

In this paper, we propose the design and fabrication on high frequency CMOS VCO for DS-UWB(Direct-Sequence Ultra-WideBand) applications using 0.18  $\mu$ m process. The complementary cross-coupled LC oscillator architecture which is composed of PMOS, NMOS symmetrically, is designed for improving the phase noise characteristic. The resistor is used instead of current source that reduce the 1/f noise of current source. The high-speed buffer is needed for measuring the output characteristic of VCO using spectrum analyzer, therefore the high-speed inverter buffer is designed with VCO. A fabricated core VCO size is 340  $\mu$ m×535  $\mu$ m. The VCO is tunable between 7.09 and 7.52 GHz and has a phase noise lower than -107 dBc/Hz at 1-MHz offset over entire tuning range. The measured harmonic suppression is 32 dB. The VCO core circuit draws 2.0 mA from a 1.8 V supply.

Key words: UWB, VCO, CMOS, PLL

#### I. 서 론

저전력, 저가격, 고속 데이터 전송을 위한 UWB (Ultra WideBand) 기술이 발전하여 상용화가 되면서 RF(Radio Frequency) 시스템 규격을 만족하기 위한 고주파 신호 발생기의 필요성이 대두되고 있다. CMOS 공정 기술이 발달하여 scaling down 됨에 따라 고주파 CMOS VCO(Voltage Controlled Oscillator) 기술의 구현이 가능해졌고, 고주파 신호를 발생하면

서 동시에 저전력을 만족하는 설계가 진행되고 있다. UWB 시스템은 의무적으로 구현해야 하는 저대역인 3~5 GHz 대역과 선택적으로 구현하는 고대역인 6~10 GHz 대역으로 구분되는데, 현재 대부분의개발 결과들은 저대역을 중심으로 이루어지고 있다. 고속 데이터 전송을 위한 UWB 시스템은 단채널 특성을 가지는 DS-UWB(Direct-Sequence Ultra WideBand) 방식과 다채널 특성을 가지는 MB-OFDM (Multi Band Orthogonal Frequency Division Multi-

한국전자통신연구원 무선홈네트워크연구팀(Wireless Home Network Research Team, Electronics and Telecommunications Research Institute)

<sup>·</sup>논 문 번 호 : 20061103-15\$ ·수정완료일자 : 2007년 1월 25일

plexing) 방식으로 구분되며, 본 논문에서는 DS-UWB 방식의 시스템에 적용 가능한 고주파 VCO의 설계 및 제작에 대해서 기술한다. DS-UWB 방식 시스템은 채널 대역폭이 3~5 GHz로 2 GHz 대역의 광대역 특성을 나타내므로 수신 입력시 많은 interferer가 들어오게된다. 이 interferer 들은 원하는 신호와 함께 하향 혼합되어 기저대역의 대역폭 바깥쪽에 나타나게 되는데, 이때 로컬의 위상 잡음 특성이 좋지 않으면 interferer 신호의 잡음 성분들이 원하는 대역폭 내로 들어오게되어 신호 왜곡 현상을 발생하게 한다. 따라서 위상잡음 특성은 일반 RF 시스템뿐만 아니라 특히 광대역 DS-UWB 시스템에서 신호의 송수신 성능을 좌우하기때문에 위상 잡음 특성의 개선이 중요하다.

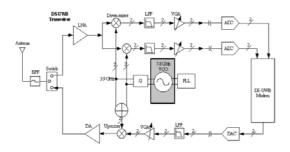

#### Ⅱ. RF 송수신기 구조

RF 송수신기는 구조가 간단하고 제작 비용도 적게 드는<sup>[1]</sup> 그림 1과 같은 직접 변환 방식 구조로 설계하였으며, 송수신 주파수와의 동일한 주파수 사용으로 인해 로컬쪽으로 유입되는 신호에 의한 pulling 영향을 줄이기 위해 동작 주파수의 두 배인 7.8 GHz 신호를 VCO에서 공급하도록 하였다. VCO에서 공급되는 신호를 2분주하여 I, Q 신호를 생성한다. DS-UWB 시스템은 캐리어 신호를 감지하여 피코넷을 인식하기 때문에 PLL(Phase Locked-Loop)에서 채널 선택 기능이 반드시 구현되어야 한다<sup>[2]</sup>.

DS-UWB 시스템에서는 BPSK 변복조를 사용하기 때문에 송신에서는 단일 path로 설계하였고, 수신에서는 멀티패스 영향을 보상해 주기 위해서 I, Q path로 구현하였다.

#### Ⅲ. 고주파 CMOS VCO 구조 및 설계

그림 1. RF 송수신기 구조

Fig. 1. RF transceiver architecture.

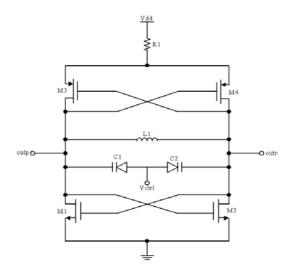

그림 2. Complementary LC VCO 구조 Fig. 2. Complementary LC VCO topology.

그림 2는 본 논문에서 사용한 Complementary LC 발진기를 나타낸다. PMOS와 NMOS가 대칭으로 구성되어 부성 저항 성분이 2배가 되어 LC tank 회로에서 발생하는 손실을 현저히 줄일 수 있고, varactor  $C_1$ ,  $C_2$ 의 전압을 조절하여 주파수를 변화시킨다. 전류원인 일반적인 능동 소자를 이용한 전류원 대신에 저항을 사용하여 전류원에서 발생하는 잡음 특성을 개선하였다. LC 발진기 구조는 고주파에서 저위상 잡음 특성을 나타내고, 대칭 구조에 의해 소자

발진기의 부성 저항은 bias 전류가 PMOS와 NMOS 에 모두 사용되기 때문에 single-sided 구조에 비해 두 배가 되며, LC tank 회로에서 들여다 본 부성 저항은 식 (1)과 같다.

의 1/f 잡음이 상향 주파수로 바뀌는 특성을 줄일 수

있다[3].

$$R_{negative} = -\frac{2}{g_{mn} + g_{mp}} \tag{1}$$

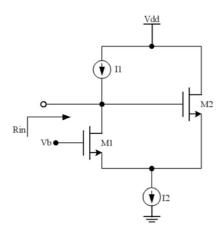

식 (1)의 부성 저항은 그림 2의  $M_1$ 과  $M_2$ 가 cross-coupled로 구성되어 그림 3과 같이  $M_1$ 의 드레인에서 바라다본 저항값이 음이 되는 구조이다.

그림 3에서  $g_{ml} = g_{m2} = g_m$ 일 경우에  $R_{in}$ 은 식 (2)와 같이 나타낸다.

$$R_{in} = -\left(\frac{1}{g_{m1}} + \frac{1}{g_{m2}}\right) = -\frac{2}{g_m} \tag{2}$$

그림 3. 부성 저항을 나타내는 회로 Fig. 3. Negative resistance circuit.

Tank 회로의 전압 크기는 식 (3)과 같이 위상 잡음 에 중요한 역할을 하다<sup>[4]</sup>.

$$laplace \triangle \omega = 10 \log_{10} \left( \frac{i_n^2/\triangle f}{q_{\text{max}}^2} \cdot \frac{\Gamma_{\text{rms}}^2}{2\triangle \omega^2} \right)$$

(3)

여기서,  $q_{\text{max}}$ 는 최대 신호 진폭을 나타내고,  $\triangle \omega$ 는 캐리어 신호로부터의 offset 주파수를 나타낸다. 그런데,  $\tan k$  신호의 크기는  $V_{\tan k} \approx I_{\tan k} \times R_{eq}$ 와 같이 공급 전류에 비례하나 공급 전류가 크면 위상 잡음이 커지는 trade-off 관계에 있기 때문에 이를 고려하여 그림 2와 같이 대칭구조이면서  $R_1$  저항을 이용하여 바이어스를 조절할 수 있도록 설계하였다. 또한  $R_1$  저항은 보통의 current mirror의 1/f 잡음을 없애기위해서 current source를 구성한다.  $M_1$ ,  $M_2$ 의 NMOS와  $M_3$ ,  $M_4$ 의 PMOS의 면적 비는 1:3으로 설계하였으며 NMOS의 면적은  $50~\mu$ m, PMOS의 면적은  $150~\mu$ m를 사용하였다. 1:1 인덕터는 대칭형 spiral 인덕터를 사용하였다.

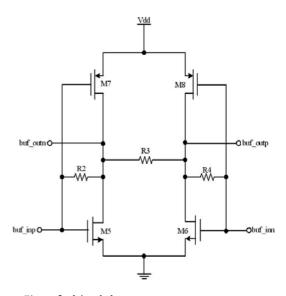

고주파 VCO의 측정용 버퍼는 고주파에서도 손실이 없이 동작을 잘 할 수 있도록 그림 4와 같이 인버터 형태의 버퍼를 설계하였다. 인버터 버퍼는 VCO와 동일한 웨이퍼상에 구현하였다.

#### IV. 고주파 VCO 구현 및 측정 결과

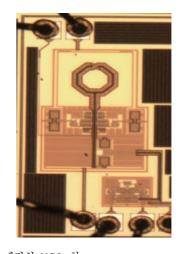

고주파 VCO는 CMOS 0.18 μm 공정을 이용하여 구현하였으며, VCO core size는 340 μm×535 μm이

그림 4. 측정용 버퍼 Fig. 4. Measurement buffer.

그림 5. 제작한 VCO 칩 Fig. 5. VCO chip micrograph.

다. 그림 5는 제작한 VCO의 bare 칩을 나타낸다.

그림 6은 COB(Chip On Board) 측정을 위해 제작한 VCO bare chip을 FR4 기판위에 실장한 것을 나타낸다.

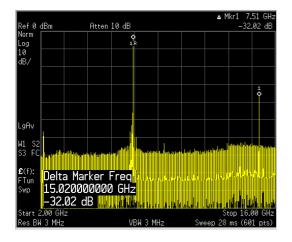

그림 7은 측정한 VCO의 하모닉 특성을 나타낸다. 1.5 V 제어 전압에서 7.51 GHz, -1 dBm 정도의 신호 특성을 나타내며, 32 dBc의 하모닉 suppression 특성을 나타낸다. 시뮬레이션 결과는 1.5 V 제어 전압에서 7.9 GHz의 특성을 나타내었으나, 측정 결과는 400

그림 6. VCO COB 측정 Fig. 6. Measurement COB for VCO.

그림 7. 고주파 VCO의 하모닉 특성 Fig. 7. Harmonic suppression characteristic.

MHz 정도의 주파수 천이가 발생했고, 이는 시뮬레이션 시 고려되지 않은 기생 성분인  $C_{sd}$ ,  $C_{db}$ ,  $C_{ss}$ 에 의한 영향 때문이다.

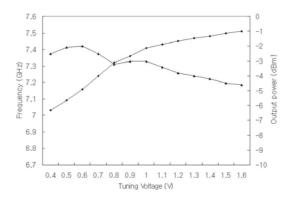

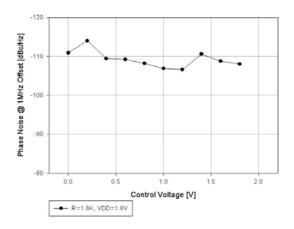

그림 8은 제어 전압에 따른 주파수 tuning 특성을 나타내고, 그림 9는 제어 전압에 따른 위상 잡음 특 성을 나타낸다.

측정한 위상 잡음은 1 MHz offset에서 -107 dBc/ Hz의 특성을 나타내고, 버퍼를 포함하여 VCO에 흐 르는 전류량은 12 mA이고, VCO 자체의 전류량은 2 mA이다.

서로 다른 고주파 VCO의 위상 잡음 성능을 비교 하기 위한 FOM(Figure Of Merit)은 식 (4)와 같이 나 타낸다<sup>[5]</sup>.

그림 8. 제어 전압에 따른 주파수 tuning 특성 Fig. 8. Frequency tuning characteristic by control voltage.

그림 9. 제어 전압에 따른 위상 잡음 특성 Fig. 9. Phase noise by control voltage.

$$FOM = 10 \log \left( \left( \frac{\omega_0}{\Delta \omega} \right)^2 \frac{1}{L(\Delta \omega)P} \right) \tag{4}$$

식 (4)의 FOM을 기반으로 본 논문에서 설계한 VCO와 다른 연구 결과를 비교한 것을 표 1에 나타내었다.

#### V. 결 론

본 논문에서는 DS-UWB용 고주파 VCO를 CMOS  $0.18~\mu m$  공정을 이용하여 설계 및 제작하였다. VCO core 만의 설계 면적은  $340~\mu m \times 535~\mu m$ 이고, 전력 소모는 3.6~mW의 저전력으로 설계하였다. 향후 주파수 tuning 회로를 첨가하고, tank 회로의 인덕터 값을 줄여 기생 성분으로 인한 주파수 천이 현상을

표 1. 고주파 VCO의 성능 비교

Table 1. The comparison of high frequency VCO performance.

|                     | 본 논문  | 참고 [6] | 참고 [7] | 참고 [8] |

|---------------------|-------|--------|--------|--------|

| 공정                  | CMOS  | CMOS   | CMOS   | CMOS   |

| 주파수                 | 7.51  | 5      | 8      | 11.22  |

| 위상 잡음<br>(dBc/Hz)   | -110  | -123   | -117   | -109.4 |

| offset 주파수<br>(MHz) | 1 MHz | 1 MHz  | 1 MHz  | 1 MHz  |

| 전력소모<br>(mW)        | 3.6   | 12     | 24     | 6.84   |

| FOM                 | 181.9 | 186.2  | 181.7  | 181.8  |

해결해야 한다.

## 참 고 문 헌

- [1] B. Razavi, RF Microelectronics, Prentice-Hall, 1998.

- [2] Matt Welborn, DS-UWB Physical Layer Submission to 802.15 Task Group 3a, IEEE P802.15-04/r-00137r0.

- [3] Ali. Hajimiri, Thomas H. Lee, "Design issues in CMOS differential LC oscillators", *IEEE Journal*

- of Solid-state Circuits, vol. 34, no. 5, May 1999.

- [4] A. Hajimiri, T. H. Lee, "A general theory of phase noise in electrical oscillators", *IEEE J. Solid-State Circuits*, vol. 33, pp. 179-194, Feb. 1998.

- [5] Peter Vancorenland, Michiel S. J. Steyaert, "A 1.57-GHz fully integrated very low-phase-noise auadrature VCO", *IEEE J. of Solid-State*, vol. 37, no. 5, pp. 653-656, May 2002.

- [6] A. Ravi, K. Soumyanath, R. E. Bishop, B. A. Bloechel, and L. R. Carley, "An optimally transformer coupled, 5 GHz quadrature VCO in a 0.18 μm digital CMOS process", in *Symp. VLSI Circuits Dig. Tech. Papers*, pp. 141-144, Jun. 2003.

- [7] D. Baek, T. Song, E. Yoon, and S. Hong, "8 GHz CMOS quadrature VCO using transformer-based LC tank", *IEEE Microw. Wireless Compon. Lett.*, vol. 13, no. 10, pp. 446-448, Oct. 2003.

- [8] N. J. Oh, S. G. Lee, "11-GHz CMOS differential VCO with back-gate transformer feedback", *IEEE Microw. Wireless Compon. Lett.*, vol. 15, no. 11, pp. 733-735, Nov. 2005.

- [9] Multi-band OFDM Physical Layer Proposal for IEEE802.15 Task Group 3a, IEEE P802.15-03/268r1.

반 보 현

1996년 2월: 경북대학교 전기공학 과 (공학사)

1998년 8월: 광주과학기술원 기전 공학과 (공학석사)

1998년 8월~1999년 6월: Ansoft Co. Application Engineer

1999년 6월~현재: 한국전자통신연

구원 선임연구원

2006년 3월~현재: KAIST 전기 및 전자공학과 박사과정 [주 관심분야] RF Transceiver Architecture, RFIC

#### 이 승 식

1996년 2월: 경북대학교 전자공학 과 (공학사)

1998년 2월: 경북대학교 전자공학 과 (공학석사)

1998년 3월~200년 7월: LG전자연 구워

2000년 8월~현재: 한국전자통신연

구원 선임연구원

[주 관심분야] RF Transceiver Architecture, RFIC

## 최 상 성

1977년 2월: 한양대학교 무선통신 공학과 (공학사)

1979년 2월: 고려대학교 전자공학 과 (공학석사)

1991년 6월: Ohio University (이학석

2000년 5월: University of Wyoming

(공학박사)

2000년 11월~현재: 한국전자통신연구원 무선홈네트워크 연구팀 팀장

[주 관심분야] UWB 통신 시스템, 신호처리, 스펙트럼공 학, 전파간섭분석