# 광통신 융합 SOP 기술

Optical Communications Convergence SOP Technology

| 광통신 | דו | 스 | ᇀᆽ |

|-----|----|---|----|

| 원동산 | 1  | ᆂ | 二二 |

임권섭 (K.S. Lim) 이종진 (J.J. Lee) 이세형 (S.H. Lee) 강현서 (H.S. Kang) 광전SOP연구팀 선임연구원 광전SOP연구팀 선임연구원 광전SOP연구팀 선임연구원 광전SOP연구팀 팀장

#### 목 차

- 1 . 개요

- Ⅱ . 광통신 융합 SOP 기술

- Ⅲ. 국내외 기술 개발 동향

- Ⅳ. 결론

광통신 융합 SOP 기술은 현존하는 다양한 통신망의 부품 및 시스템 개발에 적용 가능하고, 다양한 시스템에 호환되도록 표준화된 플러거블(pluggable) 형태로 구현이 가능하며 전기적 수동ㆍ능동 소자는 물론 광 수동ㆍ능동 소자 및 센서 소자들의 통합 패키징이 가능한 패키징 기술로 광 통신 분야를 비롯한 다양한 분야에 적용 가능한 융합된 기반을 제공하는 기술이다. 본 고에서는 SoC, SiP, MCM의 단점 및 한계를 대체할 차세대 시스템 집적기술로서의 SOP의 기술적 배경과 광통신 융합 SOP 기술 소개, 그리고 국내외 기술 개발 동향을 살펴보고자 한다.

## I. 개요

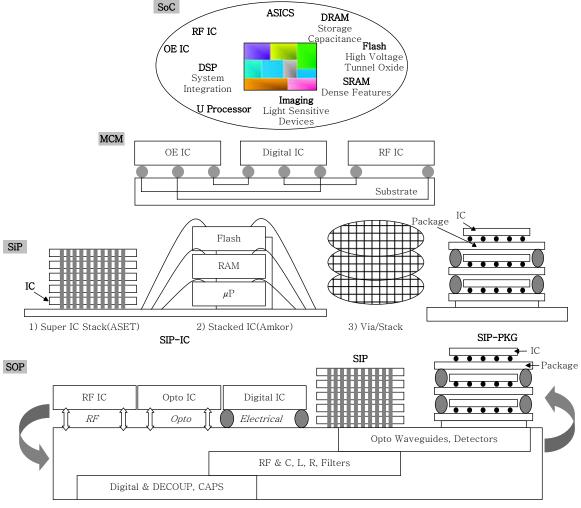

SOP 패러다임은 1990년대 중반에 미국 조지아 공대의 PRC에서 출발한 것으로, IC 레벨의 SoC와 모듈 레벨에서의 SiP 기술과 대비되는 개념으로, 모 든 필요한 기능이 단일 패키지에 집약되어 시스템의 소형화 및 융·복합화를 위해 떠오르는 차세대 패키 징 패러다임이다[1].

SOP 기술은 시스템의 60~90%를 차지하는 수 동소자를 기판 아래에 집적화하고 그 위에 능동 소 자 및 다양한 기능성 소자를 패키징함으로써 초소 형, 고집적, 다기능 시스템 구현이 가능한 패키징 기 술로 (그림 1)에서 보듯이, 기존에 개발된 센서, 저전력 모듈, SoC 소자, MEMS, RF 소자, 광소자, SiP 소자 등을 모두 포함하여 한 패키지에 집적화하여 소형화 및 다기능, 고집적 시스템 구현을 위한 설계시간과 제작시간을 단축시킬 수 있는 차세대 패키징기술로 SoC, MCM, SiP 기술의 단점 및 한계를 대체할 차세대 시스템 집적기술로서 SoC의 장점인 낮은 양산 단가와 SiP의 장점인 짧은 개발 기간 및 낮은 개발 비용과 SOP의 복합 다기능성 기판을 최대한 접목시킴으로써, 극소형 · 고기능 융 · 복합 부품에 대한 경제성을 극대화시킬 수 있는 장점을 지닌기술로 해외에서는 이미 많은 연구가 진행되고 있

(그림 1) SoC, MCM, SiP, 그리고 SOP 기술[2]

다. 〈표 1〉에서 보듯이 기존의 패키징 기반 시스템과 대비하여 SOP 기반 시스템의 주요 요소 기술은 박막 공정을 이용한 수동・능동 부품이 내장된 다기능성 기판, TSV를 이용한 3차원 수직 연결 및 다양한 부품의 융합 및 집적 기술 등이다[3].

SOP 개념을 처음 주창한 PRC의 Tummala 교수의 말에 의하면, IC의 집적도에 관한 무어의 법칙과 대비되는 시스템 집적에 대한 제2의 무어의 법칙이라 명명하고 이는 단위 체적 당 부품 또는 기능의 수로 나타내어 진다고 한다. 지난 40년 동안의 2개의 법칙의 진화과정 및 향후 전망에 대해 살펴보면, IC 집적도에 대한 무어의 법칙은 지금까지 꾸준하게 지속되어 왔지만, 시스템 집적의 경우 매우 더디게 진행되어 왔으며 향후 SOP 기술 적용으로 비약적으로 발전하게 될 것임을 시사하고 있다. 미국 조지아 공대의 PRC에서는 2005년 SOP 기술을 활용하여 cm² 당 200~300개의 부품이 내부에 내장된 모듈

이 개발되었고, 2010년경에는 약 1,000개, 그리고 2020년경에는 나노기술 등의 발전으로 인해 약 100만 개 이상의 부품이 내부에 내장되어, 반도체기술의 발전추세에서 이미 확인된 IC에 대한 무어의 법칙을 상회할 것이라고 전망하고 있다[2].

SoC의 경우 미세 반도체 공정으로 하나의 칩에 시스템을 구현하려는 노력을 계속해오고 있지만, 이는 곧 한계에 다다르게 될 것 같다. ITRS[4]에 따르면, 반도체 미세 선폭이 2012년 35  $\mu$ m에 이르게 될 것으로 전망하고 있지만, 전문가들은 지난 40여 년동안 지속되어온 무어의 법칙을 더 이상 만족할 수 없는 물리적 한계에 도달하게 될 것이라고 예측하고 있으며, 그 이유로 미세 회로 상호간의 간섭(crosstalk) 및 발열 문제를 예로 들고 있다. 따라서 반도체 회로 선폭의 미세화에 대한 연구와 더불어 패키징 기술에 대한 연구가 중요한 시점이 되었다.

일반적으로 SOP가 SiP를 포함하는 포괄적인 용

〈표 1〉 기존 시스템과 SOP 기반 시스템 비교[3]

| Building blocks                         | Traditional technology                                                       | SOP-based technology                                                                                                                                              |

|-----------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power sources                           | DC adapter, power cables, power socket                                       | Embedded thin-film batteries, microfluidic batteries                                                                                                              |

| Integrated circuits                     | Logic, memory, graphics, control, and other ICs, SoCs                        | Embedded and thinned ICs in substrate                                                                                                                             |

| Stacked ICs in<br>3D/packaged ICs in 3D | SiPs with wire bond and flip chip                                            | Wire-bonded and flip chip SiPs. Through silicon via (TSV) SiPs and substrates                                                                                     |

| Packages or substrates                  | Multilayer organic substrate                                                 | Multilayer organic and silicon substrate with TSVs                                                                                                                |

| Passive components                      | Discrete passive components on printed circuit board(PCB)                    | Thin-film embedded passives in organics, silicon wafer and silicon substrate                                                                                      |

| Heat removal elements                   | Bulky heat sinks and heat spreaders.<br>Bulky fans for convection cooling    | Advanced nano thermal interface materials, nano heat<br>sinks and heat spreaders, thin-film thermoelectric<br>coolers, microfluidic channel based heat exchangers |

| System board                            | PCB-based motherboard                                                        | Package and PCB are merged into the SOP substrate                                                                                                                 |

| Connectors/sockets                      | USB port, serial port, parallel port, slots                                  | Ultrahigh density I/O interfaces                                                                                                                                  |

| Sensors                                 | Discrete sensors on PCB                                                      | Integrated nanosensors in IC and SOP substrate                                                                                                                    |

| IC-to-package interconnections          | Flip chip, wire bond                                                         | Ultraminiaturize nanoscale interconnects                                                                                                                          |

| Packaging wiring                        | Coarse wiring<br>Line width: 25 µm<br>Pitch: 75 µm                           | Ultrafine pitch, wiring in low-loss dielectrics Line width: $2\sim5~\mu\mathrm{m}$ Pitch: $10\sim20~\mu\mathrm{m}$                                                |

| Package-to-board interconnects          | Ball grid array(BGA) bumps, tape automated bonding(TAB)                      | None                                                                                                                                                              |

| Board wiring                            | Very coarse-pitched wiring (line width/spacing: $100 \sim 200 \mu\text{m}$ ) | No PCB wiring. Package and PCB are merged into the SOP substrate with ultrafine pitch wiring                                                                      |

어로 사용되고 있으며, SOP와 SiP의 차이는 박막공 정을 이용하여 수동소자를 형성하는 기술 여부에 따라서 구분되지만 LTCC를 이용해서 수동소자를 기판 내부에 형성하는 기술이 보편화됨에 따라 SOP 개념과 SiP의 개념이 모호해진 상황이며, 수동소자가 내장된 SOP 기판 위에 3차원 칩 적층기술을 적용한 형태를 3차원 SOP라고 하고 향후 여기에 나노기술과 바이오 기술이 접목될 것으로 예상되고 있다. 또한 SOP 요소 기술을 적용하여 저전력 설계가가능하여 최근 화두가 되고 있는 그린 IT 실현을 위한 최적의 시스템 집적 기술이다.

## Ⅱ. 광통신 융합 SOP 기술

#### 1. 광통신 융합 SOP 기술

광통신 융합 SOP 기술이란 앞에서 설명한 전자기반의 SOP 기술과 광통신 기술이 융합된 새로운형태의 패키징 기술로 현존하는 다양한 코어 망(core network)의 부품 및 시스템 개발에 적용 가능하며, 다양한 시스템에 호환되도록 표준화된 플러거블(pluggable) 형태로 구현되며 전기적 수동・능동 소자는 물론 광 수동・능동 소자 및 센서 소자들의 통합 패키징이 가능한 융합된 기반을 제공하고,실리콘 공정을 기반으로 하는 광통신부품 공정에 전자회로 집적기술을 접목한 SOP 플랫폼을 기반으로

TOSA, ROSA 및 BOSA 등의 광 서브모듈을 비롯 하여 광 송수신 모듈과 PON 단말 등에 접목 가능한 기술집약적이고 저가 생산에 적합한 기술이다.

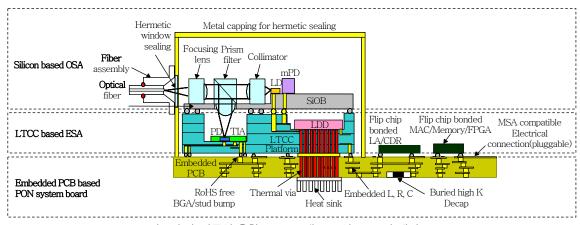

(그림 2)는 광통신 융합 SOP 기술을 적용한 광통 신 시스템을 위한 PON 단말의 개념 및 구성 요소들 을 도식화 한 것으로, 광 정렬을 위한 실리콘 기반의 광 서브모듈과 수동 소자들이 내장된 LTCC 기반 광 송수신 모듈, 그리고 임베디드 PCB 기반의 PON 단말로 구분할 수 있다. 특히 커패시터, 저항, 인덕 터, 필터 등의 수동 소자가 내장된 절연 특성이 우수 한 LTCC 기능성 기판에 캐버티(cavity)를 형성하 고, 그 안에 구동회로와 증폭기 등의 능동 전자소자 들이 실장하여, 광 송신부와 수신부를 분리함으로써 전기 · 열 · 광 누화(crosstalk)를 최소화 할 수 있는 특징을 갖는다. 광 송신 모듈의 경우, LD와 구동회 로 사이를 3D TSV로 연결함으로써 기존의 광 송신 모듈에 비해 전류 구동 길이를 최소화함으로써 신호 의 왜곡 및 누화 등을 획기적으로 개선할 수 있는 구 조이다.

이를 위한 핵심요소 기술로는, 부품의 크기를 mm 단위에서  $\mu$ m 단위까지 소형화할 수 있는 박막기술, 3차원 수직 연결을 위한 3D TSV 기술, 특히 실리콘 웨이퍼의 나쁜 절연 특성으로 인한 손실을 최소화하고 임피던스 조절이 가능한 고속 신호 전송을 위한 후막 절연 구조(polymer shield)를 갖는 TSV 기술, SiOB 및 이를 이용한 광 정렬 기술, 기생성분으로

(그림 2) 광통신 융합 SOP 플랫폼 구성 요소 및 개념도

인한 성능저하를 최소화하고 시스템 소형화를 위한 LTCC/PCB 기반 수동소자 및 광필터 임베딩 기술, 디커플링 커패시터 개발을 위한 새로운 고유전체 물 질 개발, 시스템의 소형화로 인한 발열을 효과적으로 확산시킬 수 있는 방열설계 기술, 모듈레이터, 필터, 스위치, 광원 및 광검출기, 증폭기, 구동회로 등의 광소자 및 전자소자를 실리콘 웨이퍼에 모놀리식하게 집적하기 위한 CMOS 포토닉스(CMOS photonics) 또는 실리콘 포토닉스(silicon photonics) 기술[5], [6] 및 칩-패키지-보드 통합 설계를 위한 광/전기 배선(routing) 기술[7] 등이 있다. (그림 3)은 광통 신 융합 SOP 기술을 적용한 PON용 OLT 단말의 크기를 비교한 것으로, 기존 개발된 OLT 단말에 비 해 사이즈를 백분의 일 정도인 SFP 송수신기 크기 로 줄일 수 있어, 향후 FTTH 가입자 수가 증가했을 때, 많은 가입자 수용이 수월해지고 통신국사 내에 서 하나의 단말 장치로 수십만 가입자 수용이 가능 할 것으로 사료된다.

또한 개발된 광통신 SOP 요소 기술을 바탕으로 FTTH 시장은 물론 수요가 풍부한 SAN, LAN 등 근거리 통신을 비롯, 칩 간, 칩과 보드 간, 보드 간 대용량 데이터 전송 및 HDMI[8], DVI[9], DisplayPort[10] 등과 같은 광대역 디지털 인터페이스를 위한 대용량 멀티미디어 데이터 장거리 전송 등에 응용이 가능하다. 최근 전세계적으로 HD 방송이

(그림 3) 광통신 융합 SOP 기술 적용 PON 단말

본격화되면서 고선명 멀티미디어 기기들이 속속 등장하고 있고, 데이터 전송을 위한 대역폭은 대략 10 Gb/s의 데이터 처리 속도를 요구하고 있다. 이는향후 울트라 HD 방송을 고려하면 앞으로 광대역에 대한 요구는 기하급수적으로 증가하게 될 것으로 사료된다. 이러한 광대역 서비스에 대한 요구를 충족시키기 위해서는 기존의 동선을 이용한 전송기술로는이미 한계에 이르렀다고 할 수 있으며, 그 대안이거의 무한대의 대역폭(bandwidth)과 신호 손실을 최소화 할 수 있는 광기반 광대역 전송 기술이며 광 융합 SOP 기술이 이를 실현할 수 있는 하나의 대안 이 될 수 있다.

#### 2. 광통신 융합 SOP 기술 개발의 필요성

대내적으로는 앞에는 일본이, 뒤로는 중국, 대만 이 우리나라의 기술 산업을 압박하고 있는 이 시기 에, 융·복합형 부품 및 시스템에 대한 세계 각국 산 업계의 수요가 날로 증가되고 있는 추세에 하루속히 대응해야만 이 분야에서 경쟁 국가들을 제치고 세계 일류 산업화 실현을 이룰 가능성이 있으며, 중국 광 통신산업의 급부상으로 가장 타격을 받고 있는 국내 광산업체 구제 대책이 시급하며 특히 중소 벤처기업 형태로 운영되는 국내 광산업체의 생존에 필요한 새 로운 기술전략이 필요하다. 광통신부품의 저가격화 기조를 타파, 센서 및 네트워크 부품의 기능적 다양 성 확보 등을 위하여 기술적 차별화가 될 수 있는 기 술집약적이면서도 시장성이 확보된 새로운 기술 창 출이 필요하고, 대외적으로 선진국들의 대대적인 FTTH 사업 착수에 따른 국내 광통신산업의 활성화 가 기대되는 시점이고 지난 조정기를 거쳐 광통신시 장의 거품이 소멸되고 본격적인 성장세가 예상된다. 그러나 다양한 분야의 융합 추세에 필요한 융ㆍ복합 형 부품 및 시스템에 대한 설계/제작/검증 기술과 환 경의 미비로 인하여 기술 지향적인 미래 산업의 경 쟁력이 떨어지고, 각 분야간의 상호 호환성 및 자원 집중 효율성이 떨어져 산업 전체 비용이 증가하는 문제가 제기되고 있다. (그림 4)에서 보듯이, 기존의

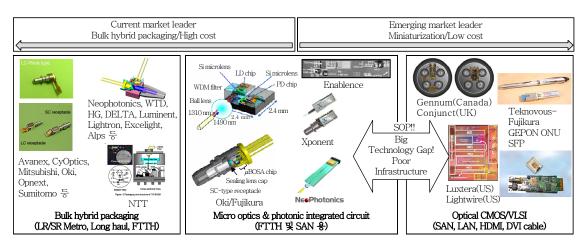

(그림 4) 광통신 부품의 기술적 접근 방법

TO-CAN 기반의 벌크(bulk)한 광학계를 사용한 광서브 모듈과 소형 광학계를 이용한 마이크로 광서 브 모듈 및 실리콘 웨이퍼에 광도파로를 형성한 평면 구조의 광 집적회로 기반의 서브 모듈 등으로 대변되는 현재 광통신 부품 시장을 점유하고 있는 광기반 광 산업체와 모듈레이터, 필터, 스위치, 광원및 광검출기, 증폭기, 구동회로 등의 광소자 및 전자소자를 실리콘 웨이퍼에 모놀리식(monolithic)하게 집적하기 위한 CMOS 포토닉스 또는 실리콘 포토닉스 기술을 이용한 선진 전자 칩 기반 업체로 양분되어져 있으며 상호간의 경쟁이 진행되고 있지만 이두 산업체 간의 기술 격차는 좀처럼 좁혀지기 어려울 것으로 보인다. 즉, 기존의 광 산업체들이 넘기힘든 CMOS 포토닉스라는 커다란 기술적 장벽이 존재한다.

< 표 2>에서 알 수 있듯이, 지금까지 주로 광통신부품 시장을 이끌어 왔던 광기반 산업체와는 달리 CMOS 포토닉스 기술 기반으로 대량생산을 통한 저돌적인 공세는 앞으로 더욱 거세질 전망이며 현재의 광통신 시장은 물론 SAN, LAN, HDMI, Display-Port 등과 같은 차세대 대용량 데이터 통신용 광 부품 시장을 잠식당할 공산이 크다.

광 기반 산업체들의 열악한 인프라와 앞서 설명 한 기술적 간극을 좁히기 위해서는 기존의 낡은 틀 을 벗어 던지고 새로운 패러다임을 도입할 필요가

〈표 2〉 광통신 서브모듈 기술 트렌드

| Current market              | Emerging market            |

|-----------------------------|----------------------------|

| Optics oriented             | Electronics oriented       |

| Still current market leader | Emerging market leader     |

| Bulky hybrid package        | Miniaturization/Monolithic |

| High cost                   | Low cost                   |

| Low productivity            | High productivity          |

| Low development cost        | High development cost      |

| Short development time      | Long development time      |

| Long reach market(telco)    | Short reach market(data)   |

있으며, 전자 기반 SOP 기술과 광통신 기술이 융합된 광통신 융합 SOP 기술이 대안 기술이 될 수 있으며, 다행히 아직 이 분야에서의 선도 기술에 대한 선진 국가 및 기업 간의 기술력 차이는 아주 크지는 않아서 융ㆍ복합형 부품 개발 환경 구축을 위한 사업을 조속히 추진하여 다양하고 복잡한 서비스 요구에적극 대비함으로써, 유비쿼터스 시대에 요구하는 다품종 고부가가치 부품시장의 선점 및 우위를 차지할수 있으리라 사료된다. 또한 시스템의 다기능화와고성능화 및 소형화, 그리고 저가격화가 요구되는디지털 융ㆍ복합화가 가속화됨에 따라 시스템 레벨의 경박단소화가 절실히 요구되고 있으며, 이를 위하여 시스템 레벨의 집적에 적합한 부품의 고밀도화및 고성능화를 위하여 표면실장부품을 기판 내부에 내장하고, 부품의 크기는 mm 단위에서 µm 단위까

지 소형화할 수 있는 박막기술을 이용한 공정 개발 이 절실하다. 아직까지 광통신 융합 SOP 기술을 적용한 상용화 제품은 아직 없으며 현재 FTTH의 상용화에 따라 요구되는 광통신 시스템의 소형화, 다기능화 및 u-Korea 구현을 위해서는 중장기적으로 관련 산업을 육성하여 세계적으로 기술 우위 선점과조기 해외 시장 개척에 나서야 할 시점이다. 아울러 SOP 기술은 소재, 공정, 설계의 분야가 종합된 차세대 패키징 기술로 관련 산업에 큰 파급효과를 줄 수 있다.

### Ⅲ. 국내외 기술 개발 동향

SOP 기술의 주요 핵심은 시스템의 대부분을 차지하고 있는 수동소자를 어떻게 최대한 집적하는가에 달려 있다. 따라서 해외 선진 연구 기관에서도 이와 같은 기술 구현에 집중하고 있으며 국내에서도 삼성전기, LG전자, 대덕전자 등이 수동소자가 내장된 임베디드 PCB 기술을 자체적으로 개발중에 있다. 현재 SOP 기술을 적용하고 있는 분야는 휴대폰, MP3 등과 같이 소형 전자기기에 제한적으로 적용되고 있는 실정이며, 해외 선진 연구기관의 경우 광,전기가 혼합된 혼성신호(mixed signal)로 처리할수 있는 시스템을 개발중에 있다.

Advanced Interconnect Technology에 따르면, '무어의 법칙'은 끝이 임박했다는 경고의 목소리가지난 십 년 동안 줄기차게 이어져 왔으며 일부 연구자는 무어의 법칙이 2010년 무렵이면 더 이상 적용되지 않을 수도 있다고 생각한다. 이러한 상황에서연구자들은 새로운 소재와 패키징 기술을 검토하고있으며, 그의 대안으로 TSV를 이용한 3차원 칩 적층 기술(3D-IC)에 대한 연구에 박차를 가하고 있다.

대용량 병렬 컴퓨터와 같은 차세대 정보 시스템 및 Tb/s급 ATM 스위칭 시스템 내에서 이루어지고 있는 보드간 및 백플레인간 전기적인 접속은 한계에 직면해 있다. 금속 케이블을 광섬유 케이블로 대체한 광접속 기술은 전기적인 접속 기술에서 나타나고 있는 한계를 극복할 수 있는 가장 유력한 방법 중의 하나이

다. 특히, 병렬 광접속 기술은 높은 처리용량, 손쉬운 시스템 집적화 등의 장점을 가지고 있기 때문에 현실 적으로 가장 좋은 방안으로 기대되고 있다. 이를 위해 대용량, 고밀도, 고속 및 저가격화의 병렬 광접속 모 듈에 대한 연구개발이 활발히 진행되고 있다.

#### 1. 북미

SOP 개념을 처음으로 제시한 PRC를 필두로 학 계에서는 CALCE와 같은 패키징 기술 연구소와 함 께 요소기술을 공동 개발하도록 산업체와 컨소시엄 을 형성하거나 산업체로부터 투자를 받아 시스템, 재료, 광학, RF, 열, 공정 기술 등 각 요소기술별로 활발한 연구개발을 진행하고 있으며 SOP 기술을 적 용한 상용화 제품은 아직 없고, 하나의 플랫폼에서 광, RF, 디지털 신호를 한꺼번에 처리 가능한 혼성 신호 시스템을 위한 혼성신호 테스트베드 실험에 성 공하였다. 또한 웨이퍼상의 패키징 기술을 개발하여 더욱 효과적인 모듈의 소형화를 위해 웨이퍼 레벨에 서의 SOP 기술을 개발하고 있으며, 초고속 칩간 광 접속을 위해, 유기기판에 박막 EEL과 MSM을 직접 집적하여 정렬 공정을 제거하고, 직접 결합하여 결 합효율을 향상시켜 소형, 저가의 광소자와 광도파로 결합 구조 연구를 진행하고 있다. 특히 다 코어 (multi-core) 프로세서를 위해 3D TSV를 이용하여 코어 간, 그리고 코어와 메모리 간 3차원 연결을 위 한 라우팅 툴에 대한 연구를 진행하고 있다.

IBM은 무선 LAN과 휴대폰 애플리케이션용 파워 앰프에 무선 통신용 로우 엔드 TSV 칩을 이미개발했으며, 300 mm 웨이퍼 기술과 65 nm 공정기술을 사용하여 3차원 적층 기술을 이용한 이 칩의양산은 2008년으로 예정되어 있고, 광 병렬 접속을위해 실리콘 기판에 TSV와 관통 캐버티를 이용하여 광 소자를 기판 안에 내장하고, 그 위에 플립칩본딩을 이용하여 구동회로나 증폭기 등을 실장하는방법으로 16배 이상의 I/O 밀도와 100배의 접속 밀도를 향상시켜 테라급의 고성능의 서버 제작 기술을연구중에 있다. 이와 같이 실리콘 공정을 사용함으

로써 리소그래피와 같은 반도체 표준 공정을 사용할 수 있고, 웨이퍼 레벨 테스트가 가능하다는 장점을 가진다.

인텔 포토닉스 기술연구소는 실리콘 광원을 집중적으로 연구하고 있다. 인텔은 CMOS 포토닉스의 구현을 위해 실리콘의 광학 특성을 향상시키려는 연구를 진행해오고 있으며, 목표는 레이저, 모듈레이터 및 검파기로 된 싱글 실리콘 칩을 만드는 데 있다. 인텔은 실험용 40 Gb/s SiGe 광 검파기를 이미개발하여 일본에서 2008년 9월에 시연한 바 있다. 또한 광 접속은 구리보다 대역폭이 넓고 더 많은 데이터 전송이 가능하기 때문에 싱글칩에 광 연결을 사용할 예정이며, 이를 위해 40 Gb/s 실리콘 모듈레이터와 웨이퍼 본딩 기술을 이용한 반복률이 40 GHz에 달하는 하이브리드 모드 로킹 실리콘 소멸레이저 개발에 성공했다.

북미 175개 업체들로 구성된 프로젝트인 AEPT는 PCB, LTCC 기반 고용량 임베디드 커패시터를 위한 고유전체 물질과 공정기술 및 톨러런스(tolerance)가 작은 임베디드 저항 제작 기술 등 수동소자가 내장된 다기능성 기판 개발을 완료했으며, 이 밖에 Infenion, IBM, AMD, Texas Instrument, Analog Device 등 기존의 상용화 기술을 보유한 업체들이 새로운 SOP 개념을 도입하여 종래의 LTCC 기반의 MCP 기술의 범위를 확대하는 방향으로 기술개발을 진행하고 있다.

#### 2. 유럽

필립스의 실리콘 기반 수동소자 집적기술 로드맵을 살펴보면, 커패시터 집적도를 2005년 mm² 당 100 nF에서 2007년 400 nF까지 향상시키고, 향후에는 높은 유전율을 갖는 물질과 새로운 공정기술을 이용한 연구를 기반으로 RF 응용뿐만 아니라 광통신, 우주항공, 의료 부분까지 적용하려는 연구가 진행중이며, 저가격화를 위해 웨이퍼가공 단계에서 모든 테스트가 가능한 공정 개발에 박차를 가하고 있다.

독일의 Fraunhofer 부설연구소인 BECAP은 SOP 뿐만 아니라 SoC와 관련된 3차원 집적 기술을

개발하고 있고, 영국의 Royal Institute of Technology는 LNA의 SOP화를 위한 연구를 진행하고 있으며, VIGOR는 SOP 기술과 수직 집적이라는 개념을 적용하여 항공우주, 자동차, 의료, 방위, 그리고 고부가가치 산업 등에 적용하기 위한 다양한 능동ㆍ수동 소자를 기판 안에 내장하고 칩이나 패키지를 수직으로 집적시키는 3차원 SOP 기술을 이용하여 능동ㆍ수동 소자가 내장되어 있는 "Cuboid"라는 3차원 모듈을 제작하고 그 상부에 폴리머를 이용한 광분배기/광결합기 및 광소자들과 클럭 등을 실장하여소형화와 저가격화를 위한 연구를 진행하고 있다.

#### 3. 아시아

일본은 IBIDEN 등 13개 업체가 참여한 SiP 컨소시엄에서 2002~2006년까지 약 75억을 투자한 "All in One" 프로젝트를 진행하였으며, 미국의 PRC에서 제시한 SOP 개념과 SiP 개념을 분리하지 않고 동일하게 사용하고 있고 학계에서도 SiP와 구별된 SOP의 연구 성과는 아직 없는 실정이다.

재료분야 강국인 일본의 Sharp, Fujitsu, Kyocera, NEC, Mitsubishi, Toshiba 등의 회사는 LTCC와 같은 기판 제작기술이 뛰어나며 칩을 적층하는 SiP 관련 특허를 미국 내에서 가장 많이 보유하고 있고, Furukawa는 Teknovos사의 ONU를 위한 EPON 제어용 SoC 칩을 이용하여 SFP 사이즈의 PON 단말을 개발하여 발표한 바 있다.

싱가포르의 STATS는 실리콘을 기판으로 사용한 SOP 모듈에 수동소자와 직접회로를 집적하기 위한 연구를 진행하고 있으며, 표준 실리콘 공정을 이용하여, 실리콘 기판에 수동소자를 집적하여 수동소자의 특성에 매우 민감한 아날로그 회로의 소형화기술 및 실리콘의 근사한 표면 특성을 이용하여 레이저 트리밍을 하지 않고, 1% 이내의 허용치를 갖는수동소자 제작에 대한 연구를 진행하고 있다.

싱가포르 국립대학에서는 나노 칩과의 인터커넥션을 위해 저가의 초미세 피치 나노 웨이퍼 레벨 패키징 기술 개발을 위해 3년간 3백만 달러를 투자하

여 미국 PRC와 실리콘 기술과 광기술을 융합한 실리콘 기반 광 융합 SOP 연구를 진행하고 있다.

#### 4. 국내

전자부품연구원은 제조공정 관점에서 본 SOP 기술은 다층 PCB를 기판으로 사용하는 SOP-L(laminated) 기술, LTCC를 기판으로 사용하는 SOP-C (ceramic) 기술, 그리고 박막기술을 바탕으로 하는 SOP-D(deposition) 기술로 분류하고, 듀플렉서필터, 세라믹적층인덕터, SAW 필터, RF front end 모듈 등의 무선이동통신용 핵심부품 및 모듈, 세라믹패키징, LTCC 관련연구, 적층필터, 듀플렉서 등의적층세라믹스 응용부품에 대한 연구를 진행하여 왔고, 2000년부터 단위적층 부품보다 여러 개의 기능을 통합하여 하나로 모듈화하는 IMT-2000용 RF front end 모듈, LNA 모듈, VCO 세라믹 모듈, PLL모듈 등의 부품의 모듈화 연구를 진행하고 있다.

한국전자통신연구원은 미래통신을 위한 초고속 무선통신용 60 GHz 밀리미터파 부품과 함께 다층 패키지로 집적할 수 있는 LTCC를 이용한 고주파용 60 GHz SOP형 광무선 송수신기 기술을 개발하였 고, 밀리미터파 대역 초고주파 집적회로(MMIC)와 이들 MMIC들을 응용한 소형ㆍ경량ㆍ저전력 송수 신기 모듈, 광집적회로, 실리콘 포토닉스, 고속 광자 기술 개발을 통해 광통신 기술과 전자 SOP 기술을 접목시킨 광통신 융합 SOP 기술을 개발하고 있다.

한국과학기술원은 13.56 MHz/UHF RFID 리더, 지상파 DMB, 고성능 MPU, 레이더 센서, Zigbee 등 SOP 기술을 적용한 시스템을 개발하였고, 기판의 적층구조, 재료, 다이/기판 적층기술, 비아, 배선, 수동소자 임베딩, 저전력 SiP 설계 등의 SOP 요소기술을 개발하고 있으며, 유관업체 SiP 개발지원, SiP 기술전파 및 교육체계를 구성하여 SOP 제작 및기술지원, 설계검증 및 DFM 환경, 자동 라우팅 환경 등의 SOP 통합 설계 환경을 구축하고 있다.

광주과학기술원은 광통신에서 사용하는 광섬유 를 활용하여 무선 신호를 전송하는 기술로 초고속 무선 데이터의 전송을 가능하게 하는 광섬유의 장점과 무선 통신기술의 장점을 결합한 광-무선 LAN 기술을 개발하고 있으며, 레이저의 순간 출력을 100조 와트로 만드는 데 성공했다. 이 기술로 펨토초라는 찰나에 자연현상을 들여다 볼 수 있게 되었고, 극한의 물리현상 실험을 통해 양성자빔, 전자빔, 이온빔, 엑스선 등의 생성이 가능해져 향후 암치료 등 레이저를 이용한 의료진단 장비 개발뿐만 아니라 마이크로 가공기술 등 초정밀 부품의 생산에도 기여 가능한 기술을 개발하였다.

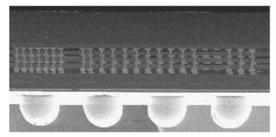

삼성전자는 종전 대규모 집적회로(LSI)와 SoC를 한꺼번에 집적한 SOP 기술을 단계적으로 개발하고 있으며, 일부 휴대용 디지털기기에 SOP를 적용하여 집적도 향상과 부피 감소를 구현하기 위한 노력을 계속하고 있고 SOP 적용 분야를 멀티미디어 휴대 폰, MP3에서 디지털 미디어, 디지털 가전 등으로 넓혀가고 있다. 또한 삼성전기는 전체 시스템의 부피를 종전보다 30% 이상 줄일 수 있는 20층 이상 세라믹 적층이 가능한 SOP 기술을 확보하고 있다. 또한 (그림 5)와 같이 TSV 기술을 이용하여 512 Mb DDR2 D램을 4개 적층한 2 Gb 대용량 D램 적층집과 이를 이용한 4 GB 모듈을 각각 개발하고, 양산화를 위한 연구를 진행하고 있다.

LG 전자는 SOP 기술을 자체 개발, 상용화를 서두르고 있고 우선적으로 휴대폰 부품에 적용해 비용 감소를 기대하고 있으며, LG 이노텍은 70여 개의 모바일 폰용 부품을 하나의 모듈로 집적한 SOP 기술을 적용하여 기존의 모바일 폰의 부피를 70% 이상 감소시킬 수 있는 제품을 개발하였다.

대덕 전자는 PCB 전문업체로 다층 PCB를 STH

(그림 5) 3D TSV 기술을 적용한 메모리 적층(삼성전자)

PCB로 생산하는 기술 개발로 40% 저가로 제조하는 기술을 개발하였고, 수동소자를 내장하기 위한 임베디드 PCB 기술을 개발하고 있다.

세계적인 패키지 전문 업체인 Amkor는 고밀도 실장을 위해 플립칩 본딩과 와이어 본딩을 혼용하여 저비용 3D 패키징 기술을 보유하고 있으며 현재 광 통신 모듈 응용을 위한 딥(deep) 비아를 한국전자통 신연구원과 공동 개발하고 있다.

### Ⅳ. 결론

IT 기술의 눈부신 발달에 힘입어, 휴대폰을 포함한 휴대기기뿐만 아니라, 가전제품에 이르기까지 소형, 고성능, 다기능을 요구하는 디지털 융ㆍ복합 제품의 수요가 급속하게 팽창하면서, 실리콘 웨이퍼에 CMOS 기술을 바탕으로 ASIC 및 메모리 기능들을함께 집적하는 기술을 기반으로 박막 능동 부품들을하나의 칩에 실장하는 기술인 SoC와 함께 디지털IC, 아날로그 IC, RF IC, 수동소자 등의 전자, 광, 센서들을 하나의 패키지 내에 구현하여 시스템 기능을제공하는 SOP가 상호 보완적인 관계로 발전할 것으로 전망된다. 이를 위해서 실리콘을 기반으로 하는실리콘에 수동소자를 집적하는 기술을 바탕으로 실리콘에 광접속을 위한 광도파로와 능동소자 집적을위한 CMOS 공정을 동시에 수행할 수 있는 실리콘기반 SOP 기술의 개발이 중요하다.

특히 SOP 기술 개발은 IT/BT/ET/NT 등 미래 산업 부문에서의 다양한 융·복합 부품 요구사항들, 즉 time-to-market, time-to-cost 및 맞춤형 부품

#### - ● 용 어 해 설 ● -

무어의 법칙: 인텔의 공동창업자인 Gordon E. Moore 의 이름을 따서 1965년에 명명된 이 법칙은 집적회로에 집적할 수 있는 트랜지스터 수가 2년마다 2배로 증가한다는 내용을 담고 있다.

SOP 플랫폼: 일괄공정이 어려운 이종 재질의 물리/화학량 센서, 전자소자 및 SoC, SiP, 광소자 등 다양한부품들을 하나의 패키지에 집적하거나 실장한 다기능통합 플랫폼이다.

의 유연성 등을 충족시킴으로써 미래 산업에 대한 산업 경쟁력을 강화시킬 수 있고, 집적도가 높고 개 발기간이 단축됨에 따라 시스템과 소프트웨어까지 접목된 고기능, 고부가가치 창출이 가능할 것으로 예상되어 광가입자/홈네트워크/USN/이동통신/광대 역 디지털 인터페이스 부품, 단말 및 시스템 등 미래 산업 전반에서 새로운 시장 선도가 가능하다고 전망 되고 있다. 또한 유비쿼터스 서비스와 연동되는 초 고속, 소형화, 센서 및 네트워크 시스템을 구축하기 위해서는 기존의 전자부품 위주의 패키징 기술에 광 통신 및 저전력 기술들이 융합된 SOP 플랫폼 기술 개발이 요구된다.

## 약어 정리

| ATM    | Asynchronous Transfer Mode                 |

|--------|--------------------------------------------|

| BT     | Bio Technology                             |

| CDR    | Clock Data Recovery                        |

| CMOS   | Complementary Metal Oxide Semiconductor    |

| DFM    | Design For Manufacturability               |

| DMB    | Digital Multimedia Broadcasting            |

| DVI    | Digital Visual Interface                   |

| EEL    | Edge Emitting Laser                        |

| ESA    | Electrical Subassembly                     |

| ET     | Environmental Technology                   |

| FPGA   | Field-Programmable Gate Array              |

| GE-PON | Gigabit Ethernet - Passive Optical Network |

| HDMI   | High Definition Multimedia Interface       |

| IC     | Integrated Circuit                         |

| IT     | Information Technology                     |

| LA     | Limiting Amplifier                         |

| LAN    | Local Area Network                         |

| LD     | Laser Diode                                |

| LDD    | Laser Diode Driver                         |

| LNA    | Low Noise Amplifier                        |

| LTCC   | Low Temperature Co-fired Ceramic           |

| MAC    | Medium Access Control                      |

| MCM    | Multi-Chip Module                          |

| MCP    | Multi-Chip Package                         |

Micro-Electro-Mechanical Systems

Monitor Photo Diode

Monolithic Microwave Integrated Circuit

**MEMS**

MMIC

mPD

| MPU  | Micro Processor Unit                |

|------|-------------------------------------|

| MSA  | Multi-Source Agreement              |

| MSM  | Metal Semiconductor Metal           |

| NT   | Nano Technology                     |

| OLT  | Optical Line Terminal               |

| ONU  | Optical Network Unit                |

| OSA  | Optical Subassembly                 |

| PCB  | Printed Circuit Board               |

| PD   | Photo Detector                      |

| PLL  | Phase-Locked Loop                   |

| PON  | Passive Optical Network             |

| RF   | Radio Frequency                     |

| RFID | Radio Frequency Identification      |

| RoHS | Restriction of Hazardous Substances |

| SAN  | Storage Area Network                |

| SAW  | Surface Acoustic Wave               |

| SFP  | Small Form Factor Pluggable         |

Silicon Optical Bench

System-in-Package

System-On-Package

Through Silicon Via

Ultra High Frequency

Trans-Impedance Amplifier

Ubiquitous Sensor Network

Very Large Scale Integration

System-on-Chip

SiOB

SiP

SoC

SOP

TIA

TSV

UHF

USN

VLSI

# 참고문헌

- [1] Rao R. Tummala, "SOP: What Is It and Why? A New Microsystem-Integration Technology Paradigm-Moore," *IEEE Transactions on Advanced Packaging*, Vol.27, No.2, May 2004, pp.241-249.

- [2] Rao R. Tummala, "Packaging: Past, Present and Future," *Int'l Conf. on Electro. Packaging Technology*, Shenzhen, China, Aug. 2005.

- [3] Rao R. Tummala and Madhavan Swaminathan, "Introduction to System-on-Package(SOP)," McGraw-Hill, 2008, pp.7-8.

- [4] ITRS web site, http://www.itrs.net.

- [5] Cary Gunn, "CMOS Photonics Technology Overview," Compound Semiconductor Integrated Circuit Symp., Nov. 2006, pp.139-140.

- [6] Richard Soref, "The Past, Present, and Future of Silicon Photonics," *IEEE J. of Selected Optics in Quantum Electronics*, Vol.12, No.6, Nov./Dec. 2006, pp.1678-1687.

- [7] Sung Kyu Lim, "Physical Design for 3D System on Package," *IEEE Design & Test of Computers*, Nov./ Dec. 2005, pp.532-539.

- [8] HDMI web site, http://www.hdmi.org.

- [9] DVI web site, http://www.ddwg.org.

- [10] DisplayPort web site, http://www.displayport.org.