BROWSE

Detail

Registered 프랙셔널 스퍼 잡음을 감소시키기 위한 위상 고정 루프

- Application No.

- 10-2015-0086013 (2015.06.17) KIPRIS

- Publication No.

- 10-2016-0149361 (2016.12.28)

- Registration No.

- 10-2376738-0000 (2022.03.16)

- Country

- KOREA

- Project Code

- 14MS1900, High Speed Long Range Wi-Fi Development for Future M2M Service, Kim Cheon Soo

- Abstract

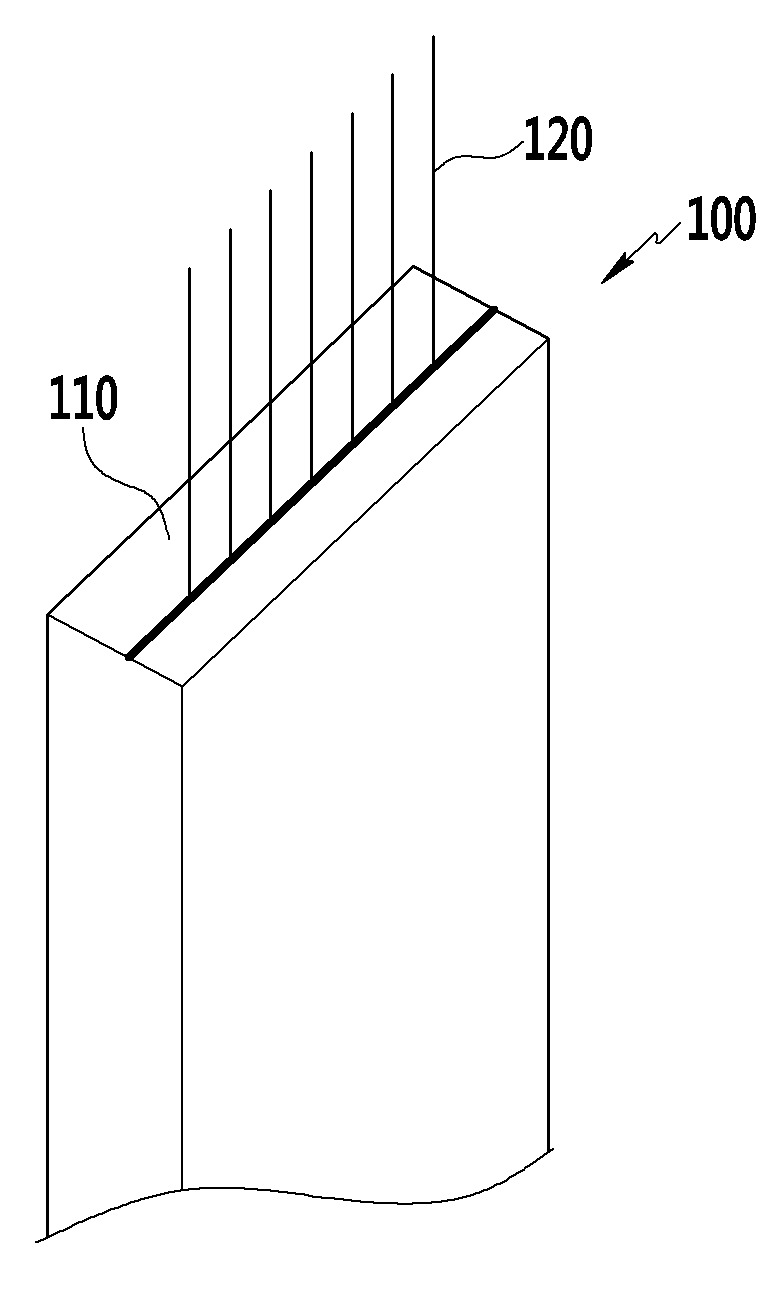

- 본 발명에 따른 기준 클록 신호에 대응하여 출력 클록 신호를 생성하는 위상 고정 루프는, 상기 출력 클록 신호로부터 제 1 시간 지연을 가지는 제 1 인터폴레이터 클록 신호를 생성하는 제 1 위상 인터폴레이터, 상기 출력 클록 신호로부터 제 2 시간 지연을 가지는 제 2 인터폴레이터 클록 신호를 생성하는 제 2 위상 인터폴레이터, 상기 제 1 및 제 2 인터폴레이터 클록 신호들 중 하나를 소정의 비율로 선택하도록 제어하는 인터폴레이터 제어 신호를 생성하는 인터폴레이터 제어기, 상기 인터폴레이터 제어 신호에 따라 상기 제 1 및 제 2 인터폴레이터 클록 신호들 중 하나를 선택하는 멀티플렉서, 상기 제 1 및 제 2 인터폴레이터 클록 신호들 중 선택된 하나를 분주하여 분주 클록 신호를 생성하는 분주기, 그리고 상기 기준 클록 신호 및 상기 분주 클록 신호 사이의 위상 차이에 대응하여 상기 출력 클록 신호의 주파수를 제어하는 디지털 제어 발진기를 포함한다.

- KSP Keywords

- Fractional Spur, phase locked, phase-locked loop(PLL), spur noise