BROWSE

Detail

Registered 범용 연산 가속기 및 그것의 동작 방법

- Application No.

- 10-2021-0029333 (2021.03.05) KIPRIS

- Publication No.

- 10-2022-0064872 (2022.05.19)

- Registration No.

- 10-2650569-0000 (2024.03.19)

- Country

- KOREA

- Project Code

- 20JS2100, Supercomuter CPU Processor Research and Development based-on Open ISA, Han Jin Ho

- Abstract

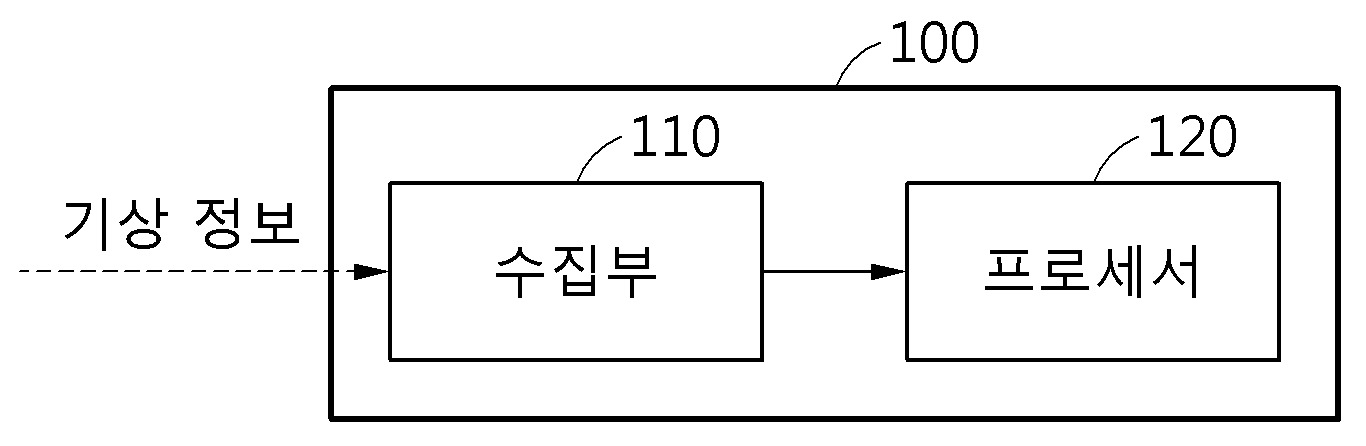

- 본 개시에 따른 범용 연산 가속기는 명령어 캐시를 포함하는 메모리, 제1 연산 동작을 수행하도록 구성된 제1 실행부, 제2 연산 동작을 수행하도록 구성된 제2 실행부, 명령어 캐시에 저장된 명령어를 페치하도록 구성된 명령어 페치부, 명령어를 디코딩하도록 구성된 디코딩부, 및 제2 실행부의 동작 상태에 따라, 명령어의 경로를 제어하도록 구성된 상태 제어부를 포함한다. 디코딩부는 명령어가 제1 타입인 경우, 명령어를 제1 실행부로 제공하고, 명령어가 제2 타입인 경우, 명령어를 상태 제어부로 제공하고, 상태 제어부는 제2 실행부의 동작 상태에 따라, 제2 타입의 명령어를 제2 실행부로 제공하거나 또는 메모리에 레지스터 파일로서 저장한다.

- KSP Keywords

- AND operation, General purpose computing, Operation method

- Family

| Status | Patent | Country | KIPRIS |

|---|---|---|---|

| Registered | GENERAL PURPOSE COMPUTING ACCELERATOR AND OPERATION METHOD THEREOF | UNITED STATES |