BROWSE

Detail

Registered 모스 구동 사이리스터 소자

- Application No.

- 10-2021-0074890 (2021.06.09) KIPRIS

- Publication No.

- 10-2021-0153554 (2021.12.17)

- Registration No.

- 10-2520077-0000 (2023.04.05)

- Country

- KOREA

- Project Code

- 19VU1700, Development of self-reliance platform in defense advanced semiconductor materials and components for weapon system, Jong-Won Lim

- Abstract

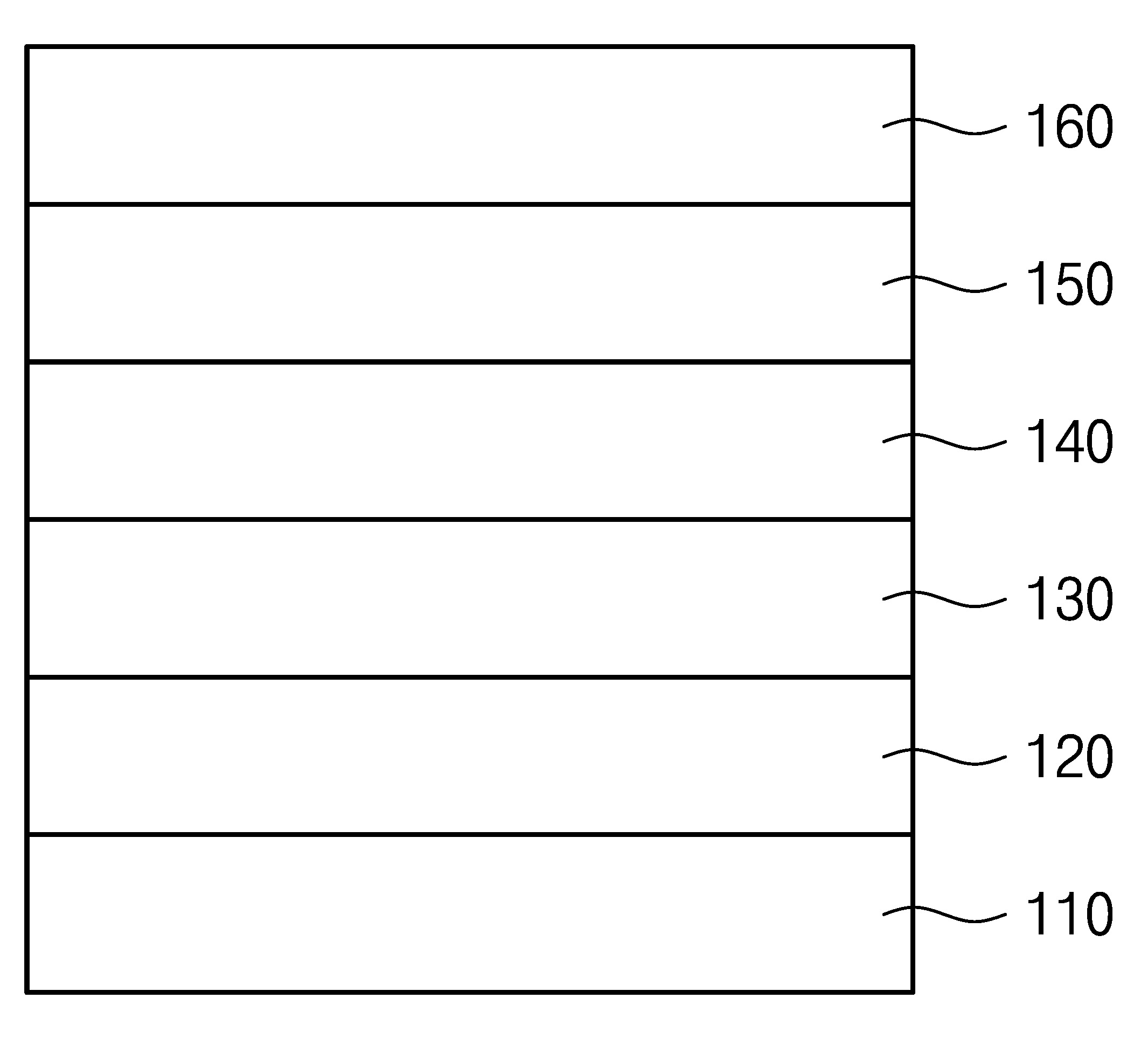

- 본 발명의 개념에 따른 모스 구동 사이리스터 소자는 마주하는 제1 면(100a) 및 제2 면(100b)을 포함하는 기판(100), 상기 제1 면(100a) 상에 배치되는 게이트 패턴들(109), 상기 게이트 패턴들(109)을 덮는 캐소드 전극(114), 및 상기 제2 면(100b) 상에 배치되는 애노드 전극(115)을 포함한다. 상기 기판(100)은 제1 도전형을 가지는 하부 에미터 층(101), 상기 하부 에미터 층(101) 상에 제2 도전형을 가지는 하부 베이스 층(103), 상기 하부 베이스 층(103)의 상부에 제공되고, 제1 도전형을 가지는 상부 베이스 영역(104), 상기 상부 베이스 영역(104)은 상기 하부 베이스 층(103)의 상면 일부를 노출시키고, 상기 상부 베이스 영역(104)의 상부에 제공되는 제2 도전형을 가지는 상부 에미터 영역(105), 상기 상부 에미터 영역(105)의 상부에 제공되고, 제1 도전형을 가지는 제1 도핑 영역(106) 및 상기 제1 도핑 영역(106)으로부터 둘러싸이는 제2 도전형을 가지는 제2 도핑 영역(107), 및 상기 상부 에미터 영역(105)의 상부의 일측면에 제공되는 제1 도전형을 가지는 제1 도핑 패턴을 포함한다. 상기 제1 도핑 패턴은 기판의 상면(100a)에 평행한 제1 방향을 따라서 상기 상부 베이스 영역(104) 및 상기 제1 도핑 영역(106) 사이에 개재된다. 상기 제1 도핑 패턴은 상기 상부 에미터 영역(105)의 상부의 타 측면에서 상기 상부 에미터 영역(105)의 상면(111)을 노출시킨다. 상기 게이트 패턴들(109)의 각각은 상기 노출된 하부 베이스 층(103)의 상면, 상기 노출된 상부 베이스 영역(104)의 상면(112), 상기 노출된 상부 에미터 영역(105)의 상면(111), 상기 제1 도핑 패턴(110), 및 상기 제1 도핑 영역(106)의 일부를 덮는다. 상기 캐소드 전극(114)은 상기 제2 도핑 영역(107)의 상면과 상기 제1 도핑 영역(106)의 상면의 일부를 덮는다. 상기 제1 도전형과 상기 제2 도전형은 서로 다르다.

- KSP Keywords

- Metal-oxide(MOX), thyristor device

- Family

| Status | Patent | Country | KIPRIS |

|---|---|---|---|

| Registered | MOS(METAL OXIDE SILICON) CONTROLLED THYRISTOR DEVICE | UNITED STATES |